## **Exercise 1: Thévenin Equivalent & RC-Circuits**

Prof. Dr. P. Fischer

Lehrstuhl für Schaltungstechnik und Simulation Uni Heidelberg

#### Recommendations

- I strongly recommend to use a mathematical program (Mathematica, Maple, SageMath,...) to solve the exercises

- For transfer functions, inspect each result:

- What happens for  $\omega \to 0, \infty$  ?

- What happens if component values go to 0 or  $\infty$ ?

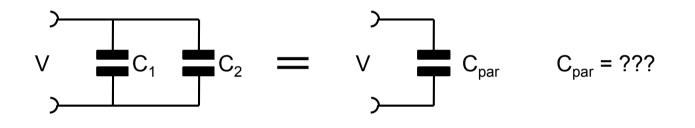

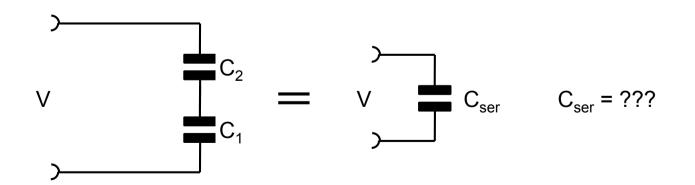

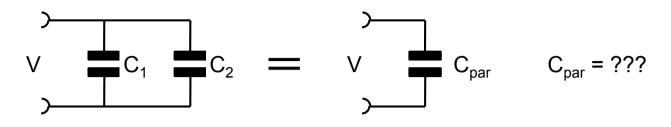

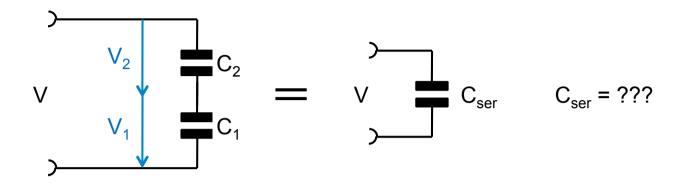

- Derive the expressions for the series and parallel connection of capacitors using

- Charge conservation

- Complex impedance & Kirchhoff's law

1. Charge conservation:  $V \times C_1 + V \times C_2 = Q_1 + Q_2 = Q_{par} = V \times C_{par} \rightarrow C_1 + C_2 = C_{par}$

### 2. Kirchhoff & complex impedance: $V sC_1 + V sC_2 = i_1 + i_2 = i_{par} = V sC_{par} \rightarrow C_1 + C_2 = C_{par}$

#### 1. Charge conservation:

Note: no charge can 'escape' the middle node, so that  $Q_1 = Q_2 = Q_{ser}$   $V = V_1 + V_2 = Q_1/C_1 + Q_2/C_2 = Q/C_1 + Q/C_2 = Q/C_{ser}$  $\rightarrow 1/C_1 + 1/C_2 = 1/C_{ser}$

#### 2. Kirchhoff & complex impedance: $V_1 ext{ sC}_1 = V_2 ext{ sC}_2$ and $V_1 + V_2 = V \rightarrow V_1 = V ext{ C}_2 / ( ext{ C}_1 + ext{ C}_2)$ $\rightarrow ext{ i}_1 = V_1 ext{ sC}_1 = V ext{ sC}_1 ext{ C}_2 / ( ext{ C}_1 + ext{ C}_2)$ $\rightarrow ext{ C}_{ser} = ext{ i} / ( ext{ Vs}) = ext{ i}_1 / ( ext{ Vs}) = ext{ C}_1 ext{ C}_2 / ( ext{ C}_1 + ext{ C}_2)$

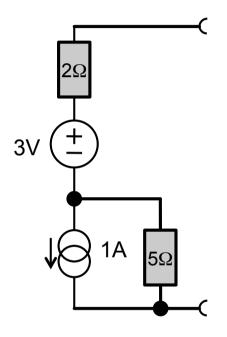

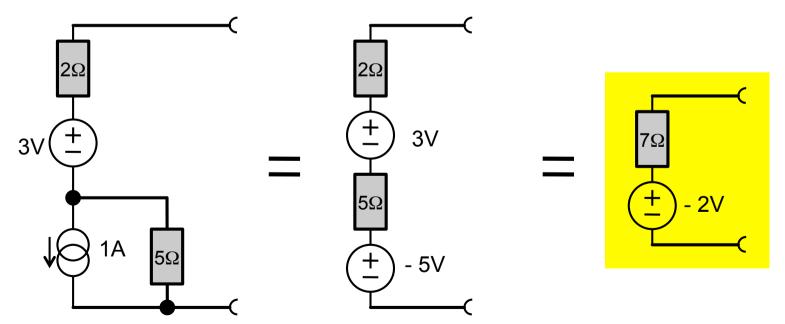

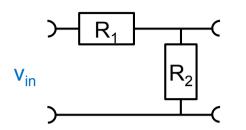

Derive the Thévenin Equivalent for the following circuit:

- Try two different methods:

- Use the Open/Short method with Kirchhoff's rules

- Convert the I-source part to a voltage source first...

#### ruprecht-karls-UNIVERSITÄT HEIDELBERG

2Ω

+

3V

1A

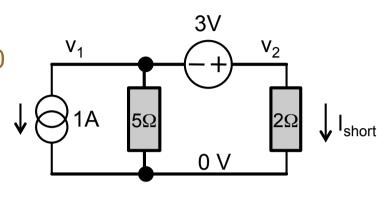

### Solution 1.1 – Kirchhoff

1. Short circuit current:

- EQ1:  $1 \text{ A} + v_1 / 5\Omega + v_2 / 2\Omega = 0$

- EQ2:  $v_2 = v_1 + 3V$

- $\rightarrow v_2 = -4/7 \vee$ •  $\rightarrow I_{short} = -2/7 \wedge$

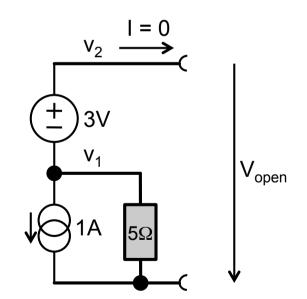

2. Open circuit voltage:

• EQ1:  $1 \text{ A} + v_1 / 5\Omega = 0$

• EQ2:

$$v_2 = v_1 + 3V$$

•

$$\rightarrow v_1 = -5 V$$

$$\rightarrow v_2 = V_{open} = -2V$$

• Source:  $V_0 = V_{open} = -2 V$ ,  $R_V = V_0 / I_{short} = 7 \Omega$

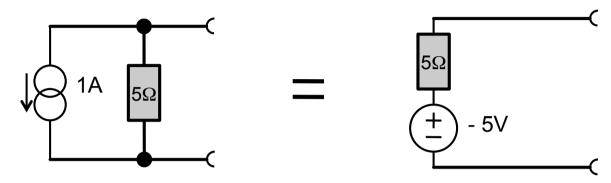

### Solution 1.1 – Thévenin Transformations

#### 1. Convert the current source to a voltage source:

2. Use this in the circuit:

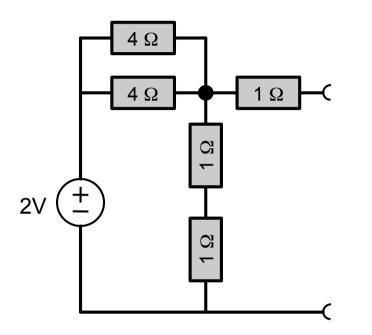

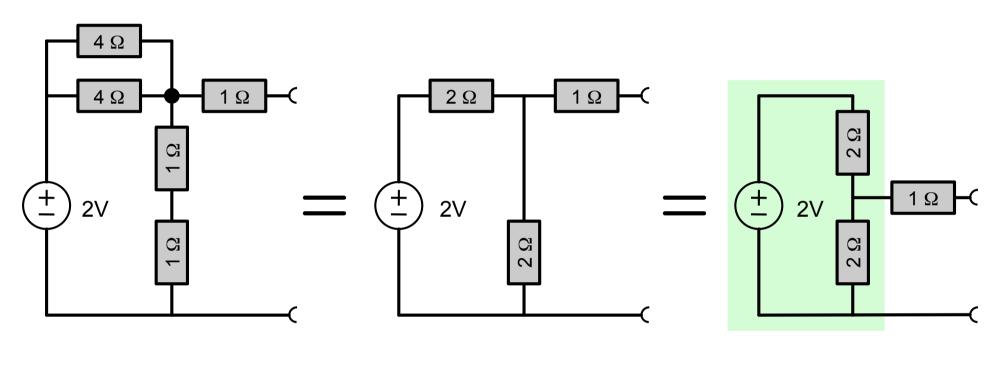

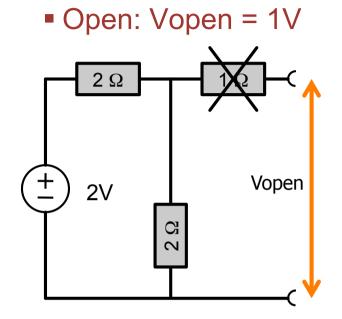

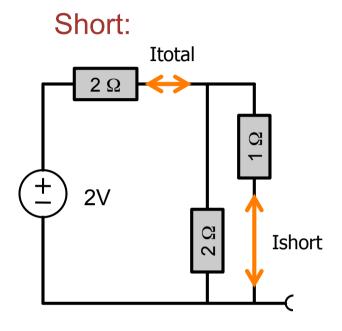

# Exercise 1.2

What is the Thévenin Equivalent of the following circuit?

- Use two methods to find the result:

- parallel / series connection of resistors and your knowledge about the voltage divider

- short/open method

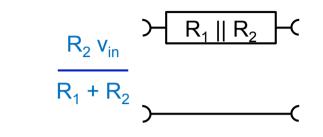

Parallel-Series Connection, Voltage Divider:

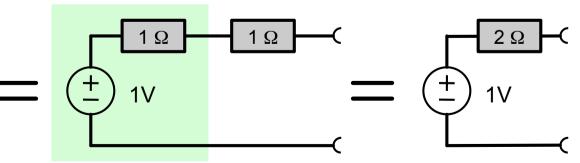

### Solution 1.2

- Rtotal =  $2\Omega + 2/3\Omega = 8/3 \Omega$

- Itotal = 2V / Rtotal = 3/4 A

- Ishort = 2/3 Itotal = 1/2 A

Zin = Vopen / Ishort

=

$$1V / \frac{1}{2} A$$

=  $2 \Omega$

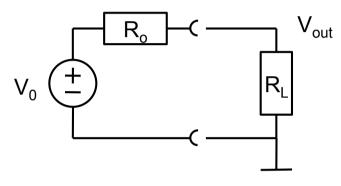

A voltage source with voltage V<sub>0</sub> and output resistance R<sub>0</sub> is loaded by a resistor R<sub>L</sub>:

- What is the output voltage V<sub>out</sub>?

- Which current flows in R<sub>L</sub>?

- What power is dissipated in R<sub>L</sub>?

- Check that noting is dissipated for  $R_L{=}0$  and  $R_L{\rightarrow}{\sim}$

- For which value of R<sub>L</sub> is the dissipation maximized?

- What is the dissipation?

ruprecht-karls-UNIVERSITÄT HEIDELBERG

$$\ln[29]:= \operatorname{Vout} = \operatorname{Vo} \frac{\operatorname{RL}}{\operatorname{R0} + \operatorname{RL}};$$

$$\ln[30]:= \operatorname{Iout} = \frac{\operatorname{Vout}}{\operatorname{RL}}$$

$$\operatorname{Out}[30]= \frac{\operatorname{V0}}{\operatorname{R0} + \operatorname{RL}}$$

$$\ln[31]:= \operatorname{Pout} = \operatorname{Vout} \operatorname{Iout}$$

$$\operatorname{Out}[31]= \frac{\operatorname{RL} \operatorname{V0}^2}{(\operatorname{R0} + \operatorname{RL})^2}$$

$$\ln[38]:= \operatorname{Table}[\operatorname{Limit}[\operatorname{Pout}, \operatorname{RL} \to \mathbf{X}], \{\mathbf{X}, \{\mathbf{0}, \infty\}\}]$$

$$\operatorname{Out}[38]= \{\mathbf{0}, \mathbf{0}\}$$

$$\ln[39]:= \operatorname{Solve}[\operatorname{D}[\operatorname{Pout}, \operatorname{RL}] == \mathbf{0}, \operatorname{RL}] // \operatorname{First}$$

$$\operatorname{Out}[39]= \{\operatorname{RL} \to \operatorname{R0}\}$$

$$\ln[40]:= \operatorname{Pout} /. \%$$

$$\operatorname{Out}[40]= \frac{\operatorname{V0}^2}{4\operatorname{R0}}$$

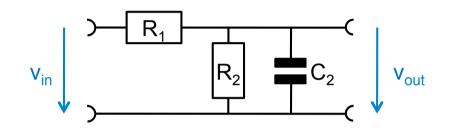

# Exercise 1.4

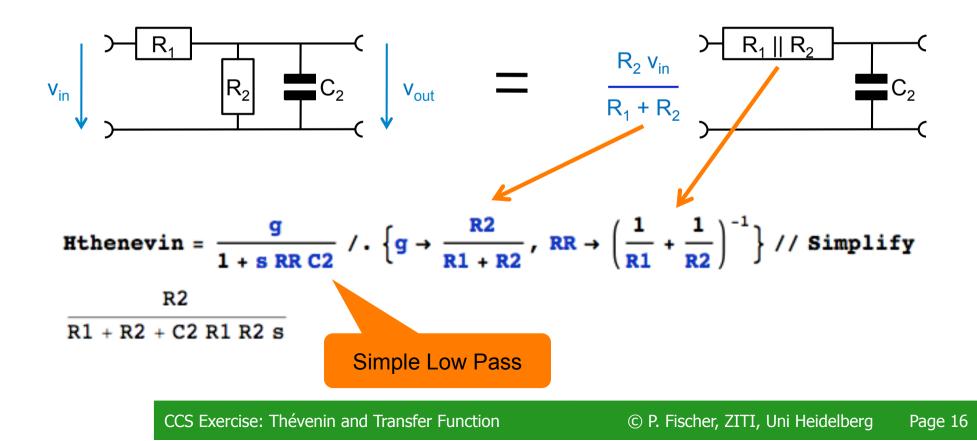

Derive the Transfer Function of this circuit:

- Use 3 different approaches:

- Treat the circuit directly (using Kirchhoff's rule)

- Consider it as a voltage divider of two Impedances. Use  $R_1$  for  $Z_1$  and the parallel connection of  $R_2$  and  $C_2$  for  $Z_2$

- Replace the (resistive) voltage divider by its Thévenin equivalent and then add the capacitor

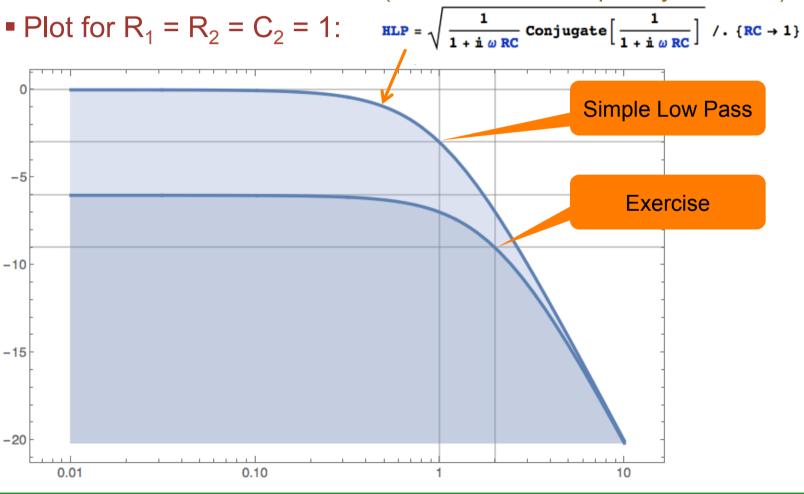

#### Make a Bode Plot

• Describe the difference to the normal Low Pass Filter

### Solution 1.4

**Direct Treatment:**

$$EQ = \frac{Vin - Vout}{R1} = Vout s C2 + \frac{Vout}{R2};$$

Solve[EQ, Vout] // First

$$\left\{ \texttt{Vout} \rightarrow \frac{\texttt{R2 Vin}}{\texttt{R1} + \texttt{R2} + \texttt{C2 R1 R2 s}} \right\}$$

$$Hdirect = \frac{Vout}{Vin} / . %$$

$$\frac{R2}{R1 + R2 + C2 R1 R2 s}$$

#### Voltage Divider:

Hdiv =

$$\frac{\mathbb{Z}2}{\mathbb{Z}1 + \mathbb{Z}2}$$

/.  $\left\{\mathbb{Z}1 \rightarrow \mathbb{R}1, \mathbb{Z}2 \rightarrow \left(\frac{1}{\mathbb{R}2} + \mathbb{S}\mathbb{C}2\right)^{-1}\right\}$  // Simplify

$$\frac{\mathbb{R}2}{\mathbb{R}1 + \mathbb{R}2 + \mathbb{C}2\mathbb{R}1\mathbb{R}2\mathbb{S}}$$

Hdirect == Hdiv

True

### Solution 1.4

- Compared to the 'simple' Low-Pass:

- The signal is attenuated by  $R_1/(R_1+R_2)$

- The time constant is lowered (i.e. the corner frequency is raised)

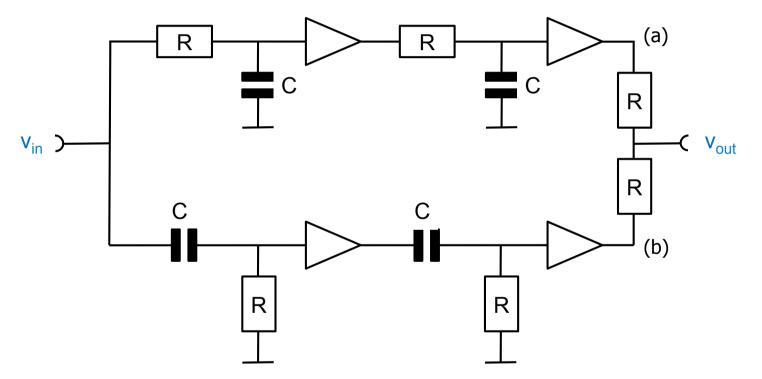

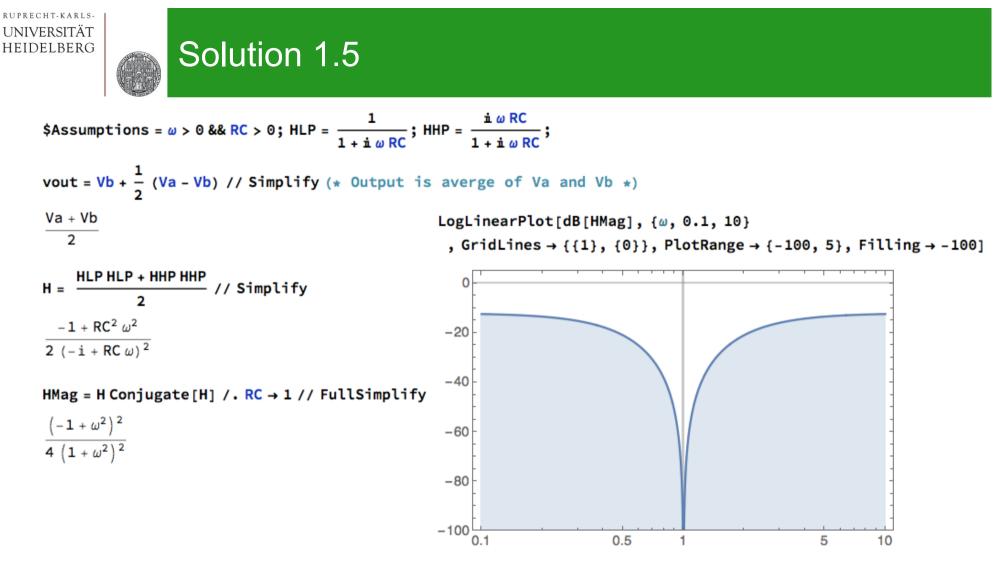

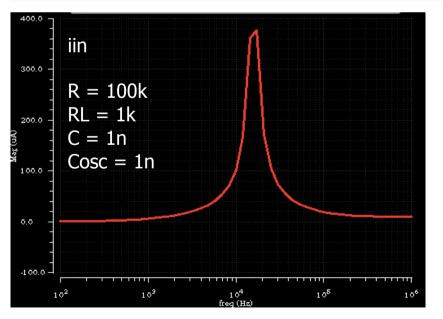

### Exercise 1.5: Notch Filter

- Consider the following circuit made of cascaded High- and Low Pass stages:

- The resistors at the output just add the signals at (a) and (b)

- What is the output signal at the corner frequency?

- Explain this by comparing amplitudes *and phases* at (a) and (b)

- At the corner frequency, the signal is fully stopped!

- This is because the phases of the two signals are ± 90°, i.e. the signals are complementary

• (A bit tricky to verify in Mathematic due to jump in ArcTan[]..)

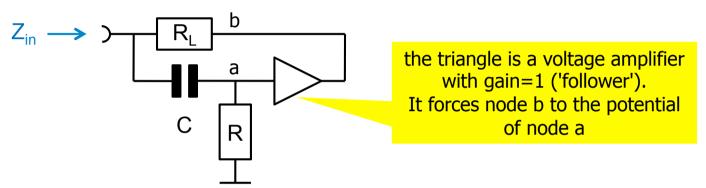

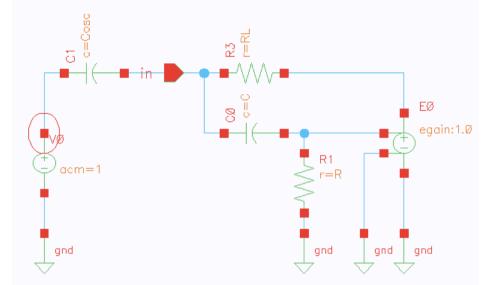

### Exercise 1.6: Gyrator (difficult)

- A 'Gyrator' can mimic inductive behaviour, while using only resistors, capacitors and amplifiers

- Consider the following circuit:

- **Calculate** the input impedance  $Z_{in} = U_{in}/I_{in}$  of the circuit

- (Use Kirchhoff's law at the input node and node a)

- For frequencies <  $1/C R_L$ , the denominator can be neglected.

- Compare the result to an inductor in series with R<sub>L</sub>

- Simulate.

- Note that R should be larger than  $R_L$  (what happens for R=R<sub>L</sub>?)

- Plot i<sub>in</sub>.

- Add another capacitor in series to produce a resonant circuit.

#### Mathematica:

- EQin = iin =:  $(vin va) \le C + \frac{(vin vb)}{RL} / . vb \rightarrow va;$ EQa =  $(vin - va) \le C =: va / R;$

- Eliminate[{EQin, EQa}, va] // Simplify

- : iin (RL + C R RL s) == vin + C RL s vin

- sol = Solve[%, iin] // First  $\left\{ \operatorname{iin} \rightarrow \frac{\operatorname{vin} + \operatorname{C} \operatorname{RL} \operatorname{s} \operatorname{vin}}{\operatorname{RL} (1 + \operatorname{C} \operatorname{R} \operatorname{s})} \right\}$

$$\frac{\text{Zgyrator}[s_{-}]}{\text{in}} = \frac{\text{vin}}{\text{in}} / \cdot \text{sol} / / \text{Simplify}$$

$$\frac{\text{RL} + \text{CRRLs}}{1 + \text{CRLs}}$$

© P. Fischer, ZITI, Uni Heidelberg Page 21