# **Exercise: Starting a Simulation**

#### Prof. Dr. P. Fischer

#### Lehrstuhl für Schaltungstechnik und Simulation Uni Heidelberg

## Starting the Simulator

ruprecht-karls-UNIVERSITÄT

HEIDELBERG

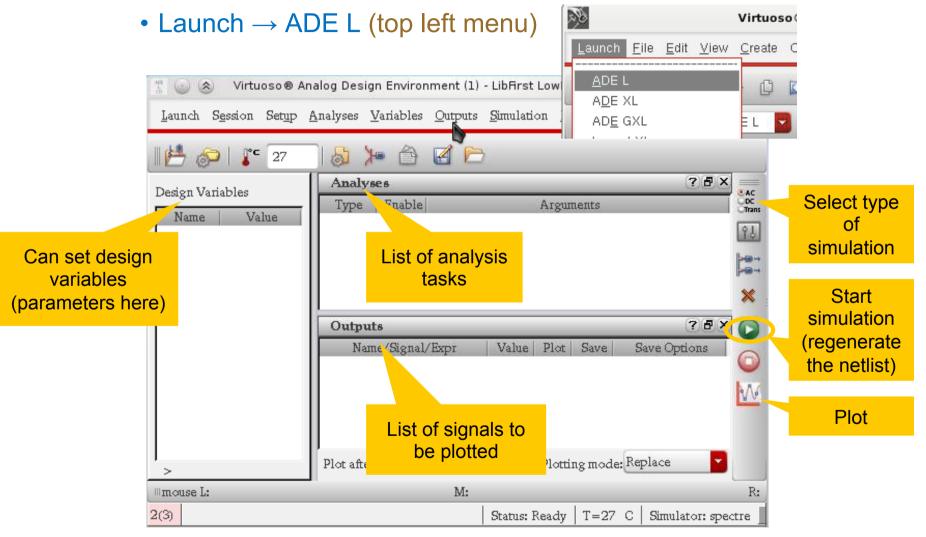

In an open schematic, start the simulator with

## Select Type of Simulation

- Open the panel

- By pressing the to button or

- In Analyses  $\rightarrow$  Choose Menu

- Choose the analysis you need (we will only use 'tran', 'dc', 'ac')

- Provide the parameters required by the analysis

Press ok

| × 💿 🗞     | Choosing Ana          | alyses V    | 'irtuoso® An |              |

|-----------|-----------------------|-------------|--------------|--------------|

| Analysis  | 🥑 tran                | 🔘 dc        | 🔘 ac         | 🔘 naise      |

|           | 🔾 xf                  | 🔍 sens      | 🔍 dcmatch    | 🔘 stb        |

|           | $\odot_{\mathrm{Pz}}$ | 🔾 sp        | 🔾 envlp      | © pss        |

|           | 🔾 pac                 | 🔾 pstb      | 🔾 pnoise     | 🔘 pxf        |

|           | O psp                 | 🔾 qpss      | 🔾 qpac       | 🔘 qpnaise    |

|           | 🔾 qpxf                | 🔘 qpsp      | 🔾 hb         | 🔘 hbac       |

|           | 🔘 hbnaise             | 🔘 hbsp      |              |              |

|           |                       | Fransient A | Analysis     |              |

| Stop Time | 2ų <b>j</b>           |             |              |              |

| Accuracy  | Defaults (errp        | reset)      |              |              |

| 🕑 conse   | ervative 📃 m          | oderate [   | 🔄 liberal    |              |

| 🔲 Transie | nt Noise              |             |              |              |

| 📃 Dynami  | ic Parameter          |             |              |              |

| Enabled 📃 |                       |             |              | Options      |

|           | OK                    | Салсе       | l Default    | s Apply Help |

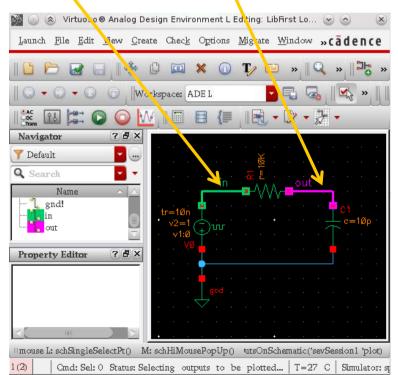

#### Select Signals to be Plotted

- In simulator window

- Select Outputs  $\rightarrow$  To be Plotted $\rightarrow$  Select on Schematic

- Select the nets (they are highlighted with different colors) to show voltages

- Select pins to show currents

- End with ESC (important!)

| 00                                 | nalog Design Environment (1) - PeFi_Play_UMC018 vorlesun 🕑 🚫                                           | ×     |

|------------------------------------|--------------------------------------------------------------------------------------------------------|-------|

| <u>aunch Se</u> ssion Set <u>u</u> | <u>up A</u> nalyses <u>V</u> ariables <u>O</u> utputs <u>S</u> imulation <u>R</u> esults <b>»cāder</b> | ۱ce   |

| 💾 🔊   🦵 27                         |                                                                                                        |       |

| C () - 1 - 1                       |                                                                                                        |       |

| esign Variables                    | Analyses ? 🖻 🛛                                                                                         | OAC.  |

| Name Value                         | Type Enable Arguments<br>1 tran ✓ 0 1u conservative                                                    | ODC   |

| C1 10p                             |                                                                                                        | ŶJ    |

| R 10K                              |                                                                                                        | 10-   |

| C2 9*C1                            |                                                                                                        | 1-00- |

|                                    |                                                                                                        | ×     |

|                                    | Outputs ? 🗗 🗙                                                                                          |       |

|                                    | Name/Signal/Expr /alu Plot Save Save Options                                                           | -     |

|                                    | 1 vout 🕜 🔲 allv                                                                                        | 0     |

|                                    | 2 vin 🗹 🔽 🔤 allv 🥿                                                                                     | W     |

|                                    |                                                                                                        | -     |

|                                    |                                                                                                        |       |

|                                    | [ <b>7</b>                                                                                             |       |

|                                    | Plot after simulation: Auto 🔽 Plotting mode: Replace 🔽                                                 |       |

| •<br>nouse L:                      | Plot after simulation: Auto Plotting mode: Replace                                                     | R:    |

Signals are listed in the lower right panel of the sim. window

### Starting the Simulation

- Press or Simulation → Netlist and Run

- A log file shows up

- If your run fails:

- Check the log file

- (Re-open it with Simulation → Output Log)

- Some common reasons for failure:

- Schematic has been changed, but not checked & saved (F8)

- Device parameters (resistor value..) are missing or wrong

- Design variables (see later) have not been set

- Circuit has severe errors (shorts..)

|                                                                                                                                                                         |                                                                                                                                               |                                                                                                                                                                                                                                                      | 10.0.0                                                                           | - 1                                                                |                                                              |                                                              |                                                                                      |                                                                      |         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------|

| tran:<br>tran:<br>tran:<br>tran:<br>tran:<br>tran:<br>tran:<br>tran:<br>tran:<br>tran:<br>tran:<br>tran:<br>tran:<br>dumber of<br>initial co<br>intrinsic<br>cotal time | time =<br>time =<br>time =<br>time =<br>time =<br>time =<br>time =<br>time =<br>time =<br>accept<br>ndition<br>tran an<br>: require<br>ulated | 752.4 ns<br>854.1 ns<br>958.3 ns<br>1.055 us<br>1.153 us<br>1.26 us<br>1.353 us<br>1.46 us<br>1.555 us<br>1.65 us<br>1.752 us<br>1.854 us<br>1.958 us<br>ed tran step<br>n solution t<br>nalysis time<br>red for tran<br>: CPU = 452.<br>mory used = | (77.8<br>(82.5<br>(87.6<br>(92.7<br>(97.9<br>s =<br>ime: CP<br>analys<br>028 ms, | *),<br>*),<br>*),<br>*),<br>*),<br>*),<br>*),<br>*),<br>*),<br>*), | step<br>step<br>step<br>step<br>step<br>step<br>step<br>step | =<br>=<br>=<br>=<br>=<br>=<br>=<br>=<br>=<br>26<br>e1<br>L m | 20 ns<br>5.728<br>7.825<br>10.72<br>14.56<br>19.74<br>8<br>.apsed<br>s, el:<br>CPU = | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>2. | d<br>01 |

| inalTime(<br>lesignPara<br>primitives                                                                                                                                   | P: writ<br>mVals:<br>: writ:                                                                                                                  | ting operati<br>writing net<br>ing primitiv<br>subcircuits                                                                                                                                                                                           | ng poin<br>list pa<br>es to r                                                    | t ir<br>rame<br>awfi                                               | nforma<br>eters<br>ile.                                      | ati<br>to                                                    | on to<br>rawf:                                                                       | raw<br>ile.                                                          | f       |

•

4

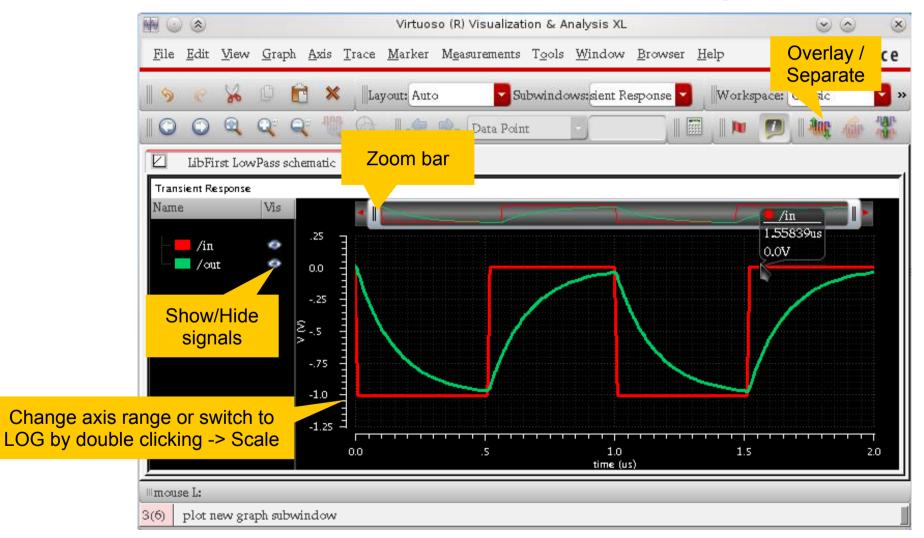

### Look at the Results

#### The waveform viewer shows all selected signals:

#### Showing More / Other Signals

- You can also add signals after the simulation using Results → Direct Plot → …

- In this menu, you can select for instance AC Magnitude and Phase

- As usual, you must then select the net and stop with ESC.

| ariables <u>O</u> utputs <u>S</u> imulation | <u>R</u> esults <u>T</u> ools Calibre <u>H</u> elp                           |  |  |  |  |  |

|---------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|

| a 🛛 🍋                                       | Plot <u>O</u> utputs                                                         |  |  |  |  |  |

|                                             | Direct <u>P</u> lot >                                                        |  |  |  |  |  |

| Main Fo <u>r</u> m                          | P <u>r</u> int                                                               |  |  |  |  |  |

| <u>T</u> ransient Signal                    | Annotate                                                                     |  |  |  |  |  |

| Transient Min <u>u</u> s DC                 | Vector 🕨                                                                     |  |  |  |  |  |

| Transient <u>S</u> um                       | Circuit <u>C</u> onditions<br><u>V</u> iolations Display<br>Reliability Data |  |  |  |  |  |

| Transient Diff <u>e</u> rence               |                                                                              |  |  |  |  |  |

| AC <u>M</u> agnitude                        |                                                                              |  |  |  |  |  |

| AC dB <u>1</u> 0                            | · · · · · · · · · · · · · · · · · · ·                                        |  |  |  |  |  |

| AC dB <u>2</u> 0                            | <u>S</u> ave                                                                 |  |  |  |  |  |

| AC Phase                                    | S <u>e</u> lect                                                              |  |  |  |  |  |

|                                             | <u>D</u> elete                                                               |  |  |  |  |  |

| AC Gain & Phase                             | Printing/Plotting Options                                                    |  |  |  |  |  |

Environment (1) - CCS2013 LowPass schematic

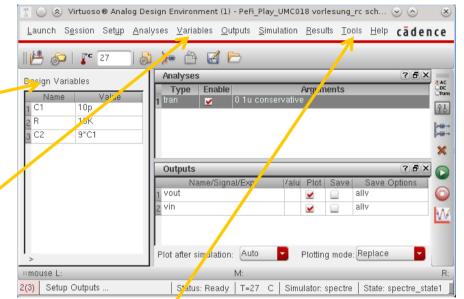

## Adding Design Variables

- You can set parameters to symbolic values ('CF', 'FREQ')

- These 'design variables' do not need to be 'declared'

- You must then

- Add the 'design variables' by hand in the lower left window or

- Use the Variables → Copy from CellView command

- You can then change the Design Variables in the simulation window and just re-run the simulation (Simulation → Run) with no need to make a new netlist

- You can also run several simulations with varying values in a Tools → Parametric Analysis

### (Copying Design Variables to the Cellview)

- You can copy the design variables and their values to the cell view with Variables → Copy to Cellview

- This helps you to remember the best values..

- Caveat:

- If you delete a variable in a schematic component, so that it is not used any more, it may still be 'saved' in the cell view and simulation will complain.

- In such a case you have to delete the variable in the simulation window and copy the new set to the cellview

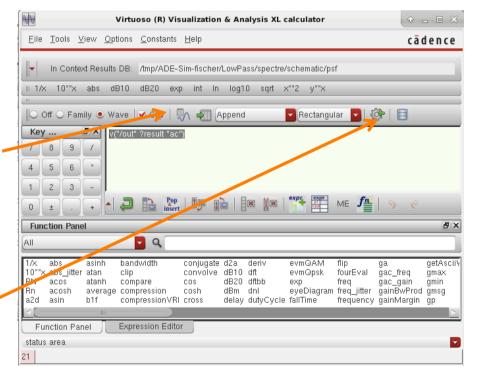

#### The WaveForm Calculator

- For more complex analysis, you can open the Waveform Calculator under Tools → Calculator

- Best select the wave you want to analyze first

- You can assemble expressions graphically (using RPN)

- Plot the result once or

- Send the expression to the outputs window so that it is evaluated every time you run a new simulation

| Outputs                         |       |          |  |  |  |

|---------------------------------|-------|----------|--|--|--|

| Name/Signal/Expr                | Value | Plot     |  |  |  |

| 1 out                           |       | <b>V</b> |  |  |  |

| 2 deriv(v("/out" ?result "ac")) |       | <b>V</b> |  |  |  |

Tools

-

Window

Calculator

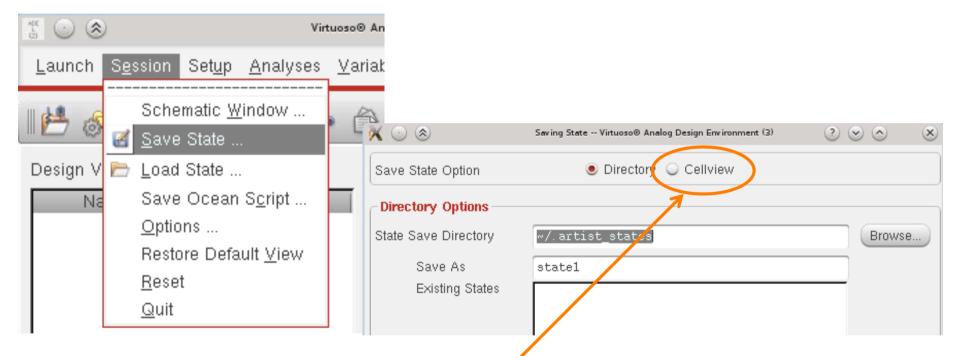

#### Saving you Simulation Settings

#### Before you leave, you can save all settings, results... under Session → Save State

- You can save to a file or to the cellview (view 'spectre\_state')

- Better save to the cellview, so that everything is in the library

ruprecht-karls. UNIVERSITÄT HEIDELBERG

## **E**XERCISES

#### Exercise 1: High Pass – AC analysis

- Use the HighPass circuit from the previous exercise

- voltage source, ground, R = 1k, C=1n

- Make sure the voltage source has 'AC Magnitude' set to 1

- Estimate the corner frequency of your circuit

- Chose an AC analysis with frequency span 2-3 orders of magnitude around the corner.

- Plot the Magnitude of the output

- Check that the -3dB point is **exactly** what you calculate!

- Change component values, predict the effect and simulate.

- Make the circuit more complicated (more Rs and Cs)

## Exercise 2: High Pass & Rectangular Pulse

- Now use a rectangular pulse generator (vpulse)

- Chose the frequency much slower than the RC time

- How does the output waveform look like ?

- When has the signal decreased to 1/e of the input step?

- Is this what you expect from the component values?

- Double the resistor and check what happens!

## Exercise 3: High Pass & Sine Input

- Replace the rectangular generator by a sine wave generator ('vsin')

- Set the *delay time* and *offset* to 0, the *amplitude* to 1V

- Calculate the corner frequency (in Hertz!)

- Check the output for a frequency ~10 x lower or ~10x higher than the corner

- What is the output amplitude *exactly* at the corner frequency?

- What is the phase shift between input and output at the corner frequency?

- Try to run a parametric analysis, changing the value of the capacitor (or the resistor)