# Exercise: Current Mirrors

### Prof. Dr. P. Fischer

### Lehrstuhl für Schaltungstechnik und Simulation Uni Heidelberg

### Exercise 1: Dynamic Regulation

- Draw a diode connected NMOS

- Connect a large ,extra' capacitance to the gate (some pF) with an *initial condition* of 0 V

- Use a transistor 'n\_18\_mm' from the UMC library 'UMC\_018\_CMOS'. Connect bulk and source.

- Set the initial condition ('IC') in the properties of the capacitor

- Send a small current I<sub>in</sub> (nA-µA) into the ,diode'

- Perform a transient simulation

- Observe the Input = Gate = Drain Voltage

- Use different initial conditions (0...1.8V, Parametric sweep!)

- Understand how the equilibrium point is reached!

- Vary I<sub>in</sub>!

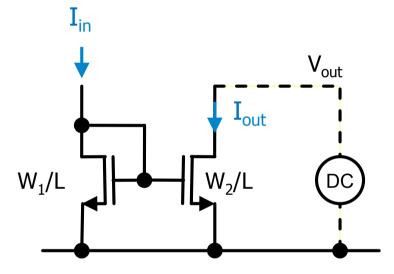

## Exercise 2: A First Mirror

• Draw the following *current mirror*, with  $W_1 = W_2 = 1 \mu m$ . Use for instance L = 0.5 $\mu m$  and  $I_{in} = 10 \mu A$

- Sweep the output voltage V<sub>out</sub> and observe the current I<sub>out</sub>.

- When is I<sub>out</sub> = I<sub>in</sub> *exactly*? Why?

- Try another input current!

- Change W<sub>2</sub>!

- For fixed I<sub>in</sub>, W<sub>1</sub>, W<sub>2</sub>, vary L (same in both MOS).

- Explain what you see!

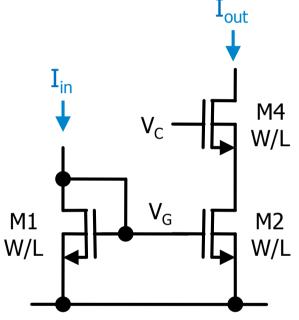

## Exercise 3: A Better Mirror

- The output current varies with V<sub>out</sub> (i.e. the output resistance is not infinite) due to the Early Effect in M2.

- Try the following circuit:

- Connect bulk and source in all MOS

- Start with  $V_c = 1.2V$

- Use I<sub>in</sub> = 1uA

- Sweep V<sub>out</sub>

- How is the output resistance now? (You may simulate the ,simple' mirror of the previous exercise in parallel for comparison)

- Calculate the small signal output resistance!

- You only need to consider M2 and M4 (because  $V_G$  is constant)

- Vary V<sub>C</sub> (from 0V to 1.8V) and see what happens

- What is the 'ideal'  $V_C$  ?

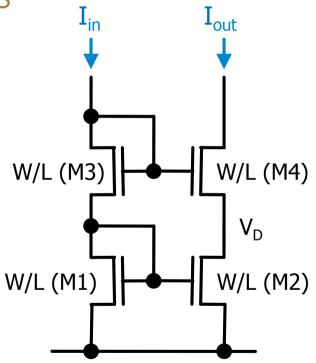

## Exercise 4: A Mirror with Better Matching

- Unfortunately, the previous circuit does NOT reproduce I<sub>in</sub> exactly. Why?

- Try this circuit (which does not need V<sub>C</sub> and more):

- Connect bulk and source in each MOS

- It is called the ,stacked mirror'

- Sweep V<sub>out</sub>

- Do currents match?

- What is r<sub>out</sub> ?

- Where is the saturation ?

• What is the drain voltage V<sub>D</sub> of M2? Is that optimal?

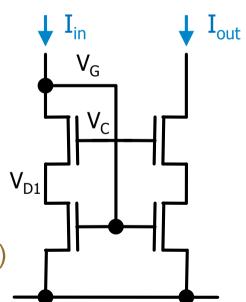

## Exercise 5: The Low Voltage Mirror

- In the stacked mirror of the previous exercise, the drain voltage V<sub>D</sub> of the current source M2 is fixed by the diode connection of M1.

- This is simple, but provides a too high voltage (by ~V<sub>T</sub> !)

- The following circuit connects the diode differently:

- Understand that the gate voltage V<sub>G</sub> still stabilizes to the 'correct' level!

- We now need to find  $V_{\rm C}$

- Sweep  $V_C$  from 0.4 to 1.4V in steps of 0.2V

- What is a good choice?

- Why do very low voltages fail (check V<sub>G</sub> !)

- What happens at high voltages? Why? (this is tricky to understand... Look at V<sub>D1</sub>...)

- Note that the 'best'  $V_{\rm C}$  depends in  $I_{\rm in}$

RUPRECHT-KARLS-UNIVERSITÄT

HEIDELBERG

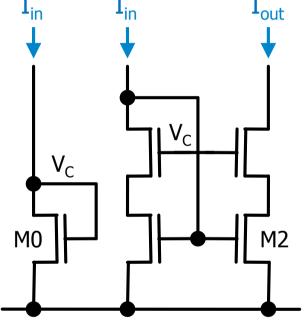

## Exercise 6: The Low Voltage Mirror

- The required optimal cascode voltage V<sub>C</sub> can be generated automatically by a diode connected MOS M0 with different geometry than the others:  $I_{in} \qquad I_{in} \qquad I_{out} \qquad I_{out} \qquad I_{in} \qquad I_{out} \qquad I_{out} \qquad I_{in} \qquad I_{out} \qquad I_{out} \qquad I_{in} \qquad I_{out} \qquad I_{in} \qquad I_{out} \qquad I_{in} \qquad I_{in} \qquad I_{out} \qquad I_{in} \qquad I_{in$

- We assume that we have a second input current I<sub>in</sub> available (boths I<sub>in</sub>s are equal)

- Calculate k so that M2 is just saturated.

- Use the *large signal* model in strong inversion with no Early effect

- Simulate the circuit

RUPRECHT-KARLS-UNIVERSITÄT

HEIDELBERG

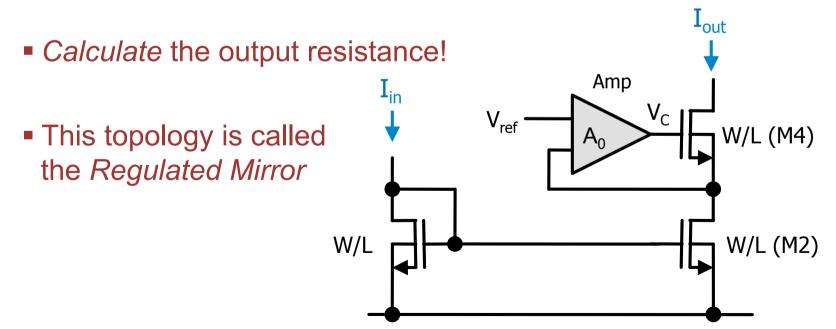

### Exercise 7: An *Even* Better Mirror

- The key trick is obviously to keep the drain voltage of M2 very constant irrespective of the output voltage.

- This can be done with an active circuit (with an amplifier):

- Amp amplifies the difference of the two input voltages by A<sub>0</sub>

- Where is the positive/negative input for table operation?

- Simulate the circuit. Use a voltage controlled voltage source vcvs from the analogLib for Amp with A<sub>0</sub>=1000