RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

# Exercise: The MOS Transistor

#### Prof. Dr. P. Fischer

### Lehrstuhl für Schaltungstechnik und Simulation Uni Heidelberg

CCS Exercise: MOS Transistor

© P. Fischer, ZITI, Uni Heidelberg Page1

### Exercise 1: Simple MOS (Level 1 model)

- We want to simulate a MOS with a very simple model (as the formula shown in the lecture)

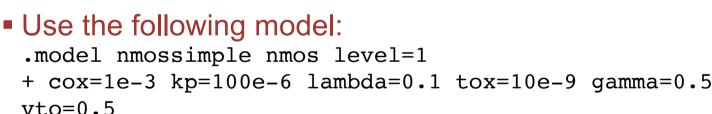

- Create a schematic which allows you to set V<sub>G</sub> and V<sub>D</sub> of a MOS:

- Use 'nmos4' from 'analogLib'

- Attach the model 'nmossimple' (see diode exercise. Add path!)

Plot

RUPRECHT-KARLS-UNIVERSITÄT

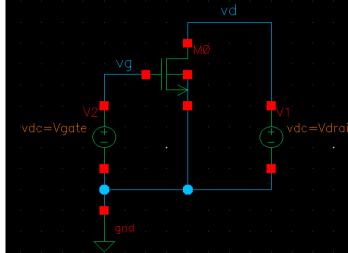

- $I_D$  for  $V_G$ =0..2 V with  $V_D$ =2V (Transfer characteristic)

- $\sqrt{I_D}$  for V<sub>G</sub>=0..2 V with V<sub>D</sub>=2V (Sqrt of transfer characteristic)

- $I_D$  for  $V_D=0..2$  V with  $V_G=1V$  (Output characteristic)

- Transfer (linear y scale)

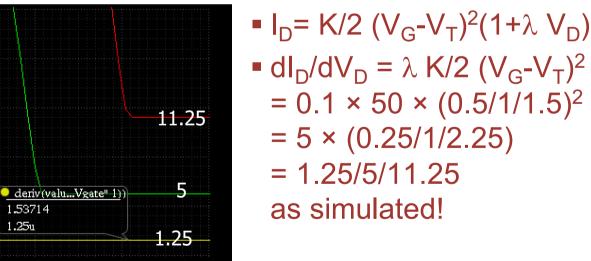

- Current at  $V_G = 1.5V$  is  $I_D = K/2 (V_G - V_T)^2 (1 + \lambda V_D)$   $= 50 \times 1 \times (1 + 0.1 \times 2) \mu A$  $= 50 \times 1.2 \mu A = 60 \mu A$

- Sqrt(..) plot shows exact quadratic behaviour ('level 1 model')

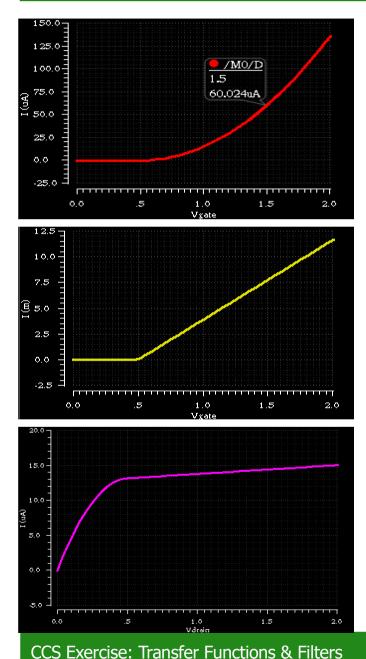

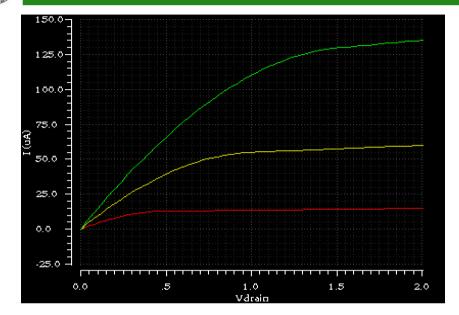

- Output Char. shows Early effect

- Current at kink is  $I_D = K/2 (V_G - V_T)^2 (1 + \lambda V_D)$ = 50 × 0.5<sup>2</sup> × (1+0.1×0.5) µA = 12.5 × (1.05) µA

- Sweep  $I_D$  for  $V_D=0..2$  V with  $V_G=1V$ , 1.5V, 2V

- What are the slopes at high drain voltages ?

- Do they correspond to what you expect ?

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

20.0

16.0

12.0

8.0

4.0

0.0

0.0

3

1.53714 1.25u

1.0

Vdrain

1.5

2.0

Current increases

CCS Exercise: Transfer Functions & Filters

.5

#### RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

### Exercise 3: A real MOS

- Now use the model 'nmos' provided in the file MOSLib.lib in moodle (this MOS should be operated below 2V)

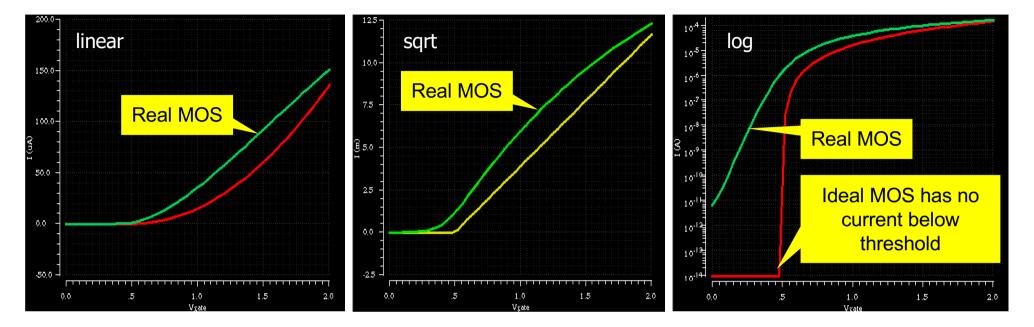

- Compare the transfer curves of a 'nmossimple' and 'nmos'

- Are they both exactly quadratic?

- What happens at low gate voltages (below threshold)? Do a logarithmic plot!

- Real MOS is not quadratic

- Velocity saturation at high Gate voltages

- Current >0 in weak inversion (below threshold)

### Exercise 4: Sizing the MOS

- Set the properties W and L of both types of MOS to WL

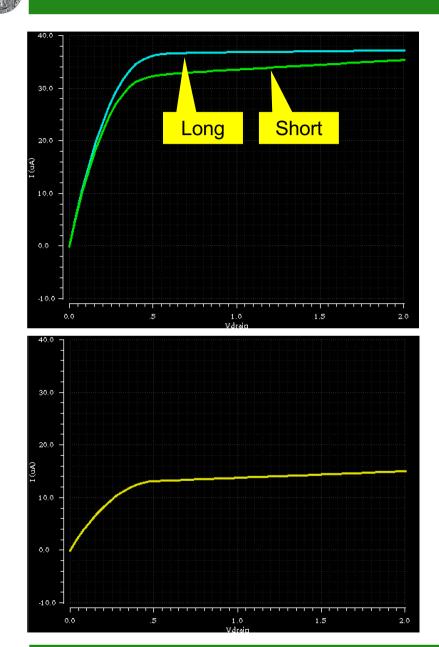

- Compare the output characteristics for WL=1u and WL=10u for both MOS

- Is there a change in output resistance if you change the geometry?

ruprecht-karls-UNIVERSITÄT HEIDELBERG

For the real MOS, the output resistance increases, when L is increased

For the 'nmossimple', there is NO difference (both curves are the same).

This model is clearly too simplistic!

CCS Exercise: Transfer Functions & Filters

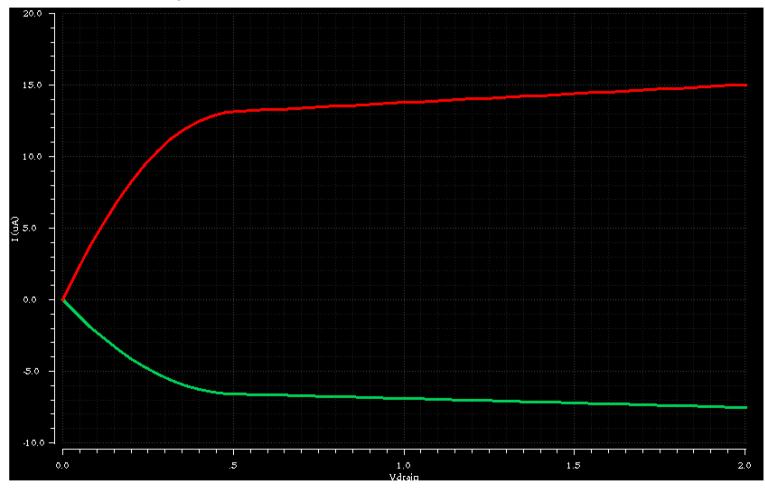

### Exercise 5: PMOS

- Simulate transfer and output characteristic for a PMOS

- Note that the source of the transistor is now ,on top'

- Gate and drain must be negative with respect to source

- Simulate in parallel a NMOS of the same size.

- Plot the drain current of NMOS and PMOS simultaneously.

- How big is the difference?

- Does that fit the model?

#### Here for simple models:

#### Ratio is exactly 3, the ratio of the kp parameters

CCS Exercise: Transfer Functions & Filters

© P. Fischer, ZITI, Uni Heidelberg Page 11

### Exercise 6: Formulae match...

RUPRECHT-KARLS-UNIVERSITÄT

HEIDELBERG

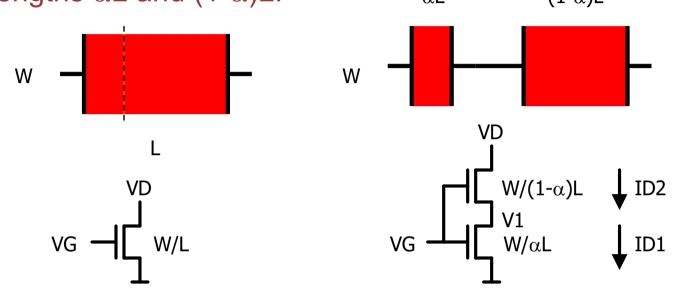

• A MOS with width W and length L is cut in two devices with lengths  $\alpha L$  and  $(1-\alpha)L$ :  $\alpha L$   $(1-\alpha)L$

- The series connection must behave as the single device!

- Assume a large VD. In which regimes do the 2 MOS operate (lin. / sat.?). Write down the formulae for ID1 and ID2

- The currents must be equal. Find α. Then find ID1 (=ID2)

- Is this the current of the single MOS?

- How large is V1 for  $\alpha$ =5/9 ?

ruprecht-karls-UNIVERSITÄT HEIDELBERG

### Solution 6:

In[63]:= ILin[Vgs\_, Vds\_] = (Vgs - Vt) Vds -  $\frac{1}{2}$  Vds<sup>2</sup>; ISat[ $Vgs_$ ,  $Vds_$ ] =  $\frac{1}{2}$  (Vgs - Vt)<sup>2</sup>;  $\ln[91] = EQ1 = \frac{W}{\alpha L} ILin[VG, V1] = \frac{W}{(1 - \alpha) L} ISat[VG - V1, VD - V1] // Simplify$ Out[91]=  $\frac{W(V1^2 - 2V1(VG - Vt) + (VG - Vt)^2\alpha)}{L(-1 + \alpha)\alpha} = 0$  $\ln[67] = \alpha \text{ sol} = \alpha / . \text{ First@Solve}[EQ1, \alpha] (* \text{ find } \alpha *)$ Out[67]=  $\frac{-V1^2 + 2 V1 VG - 2 V1 Vt}{(VG - Vt)^2}$  $\ln[69] = I2 = \frac{W}{\alpha I}$  ILin[VG, V1] /.  $\alpha \rightarrow \alpha$ sol // Simplify (\* Find current \*)  $Out[69] = \frac{(VG - Vt)^2 W}{2 I}$ ln[71]:= I2 ==  $\frac{W}{L}$  ISat[VG, VD] // Simplify (\* Compare to single MOS \*) Out[71]= True In[72]:= \$Assumptions = VG > Vt; In[73]:= V1sol = V1 /. First@Solve[EQ1, V1] // Simplify Out[73]= - (VG - Vt)  $(-1 + \sqrt{1 - \alpha})$  $\ln[74]:=$  V1sol /.  $\alpha \rightarrow 5/9$  $Out[74] = \frac{VG - Vt}{3}$

CCS Exercise: Transfer Functions & Filters

© P. Fischer, ZITI, Uni Heidelberg Page 13

### Exercise 5: Drain Capacitance

- Charge the drain capacitance of the 'real' MOS to determine its C(V) curve

- Set  $V_G$  to 0 to turn the drain current off

- Add a small cap in parallel to define the start voltage 0 V

## 1: Transfer Characteristic & Transconductance

- For an NMOS of W=L=1µm with V<sub>BS</sub> = 0, keep the drain at 1.8 V and sweep the gate voltage from 0 to 1.8 V. This is the *transfer characteristic* of the MOS.

- Observe the drain current

RUPRECHT-KARLS-UNIVERSITÄT

- Plot the square root of the current. Do you find a straight line as expected?

- Plot the current in log scale. Can you see the sub-threshold region?

- What is the transconductance at  $V_{GS} = 1V$  (make a derivative!)?

- Make a parametric sweep changing W from 0.24µm to 2µm

- Is the current proportional to W?

- Repeat this for a L-sweep (start with 180nm)

- Plot the transfer curve for two different values of V<sub>BS</sub>, for instance 0 V and -2 V

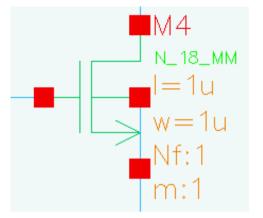

### Exercise 1: NMOS in Linear Region

- Use an NMOS transistor of type N\_18\_MM from library UMC\_18\_CMOS with W=L=1µm

- Connect

RUPRECHT-KARLS-UNIVERSITÄT

- source and bulk to ground

- the gate to 2 V

- Sweep V<sub>DS</sub> from -0.1V to 0.1 V and observe the current

- Extract the resistivity of the channel

- Double W or L and simulate & extract again.

- Are the results as expected ? Compare W=L=1µ and W=L=2µ!

- Now sweep the *gate* voltage from 0.6 V to 2 V. Explain!

- Now sweep the *drain* voltage from 0V to 1V. Verify the saturation point for a few gate voltages.

- What happens if you sweep the drain voltage from -1V on?

### Exercise 3: Output Characteristic, Saturation

- Now plot the output characteristic, i.e. I<sub>D</sub> as a function of V<sub>DS</sub> for a fixed V<sub>GS</sub> (for instance V<sub>GS</sub> = 1.0 V)

- Can you see the linear region and the saturated region?

- Extract the output resistance for instance for  $V_{GS}$ =1.8V and  $V_{DS}$ =1.8V (derivative!).

- Plot the output characteristic for V<sub>GS</sub> =0..1.8V in 0.2V steps

- Observe how the current changes

- Observe how the saturation voltage changes

- Observe how the output resistance changes (Early voltage ?)

- Now use two NMOS with different W (for instance 0.5µm and 2µm).

- Search for gate voltages so that the currents for a given  $V_{\text{DS}}$  (for instance for 1.8 V) are similar.

- Compare the output characteristics & saturation voltages

RUPRECHT-KARLS-UNIVERSITÄT