RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

## **Current Mirrors**

Our first 'useful' circuit

(you will understand later THAT this is REALLY useful)

P. Fischer, ZITI, Uni Heidelberg, Seite 1

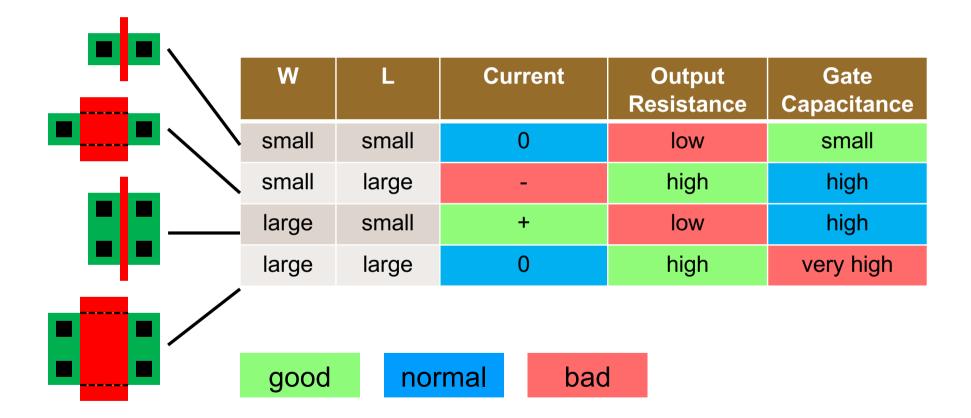

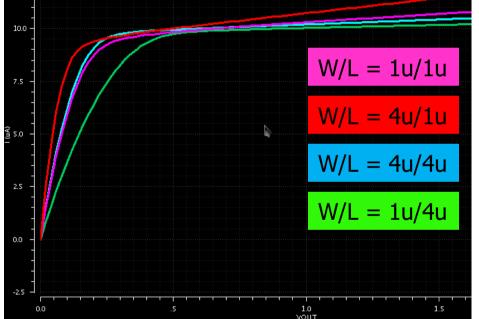

#### Reminder: Effect of Transistor Sizes

• *Very* crude classification (at constant V<sub>GS</sub>):

There is no 'perfect' size – all depends on what we need!

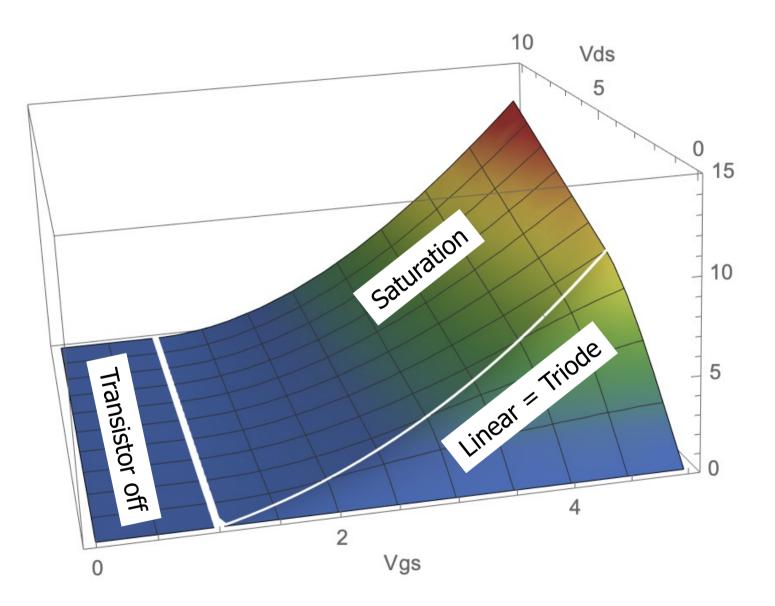

#### Reminder: Transistor Characteristics

## Reminder: Threshold and Saturation Voltage

$$I_D = \frac{K}{2} \frac{W}{L} (V_{GS} - V_T)^2 = \beta (V_{GS} - V_T)^2$$

$$V_{D,Sat} = V_{GS} - V_T = \sqrt{\frac{I_D}{\beta}}$$

$$V_{D,Sat} \qquad V_D$$

$$V_{CS} = V_T + V_{D,Sat}$$

$K \approx 100 \,\mu A/V^2, \, W \approx 1 \,\mu m, \, W \approx 0.2 \,\mu m \quad \rightarrow \quad \beta \approx 250 \,\mu A/V^2$

For  $I_D = 10 \,\mu A \quad \rightarrow \quad V_{D,Sat} \approx 0.2 \, V$

This is all only valid for strong inversion (at 'large' currents)

V<sub>D,Sat</sub> increases with larger current (with the \sqrt{)}

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

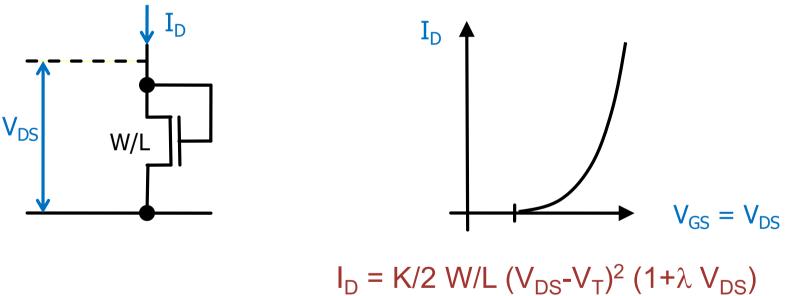

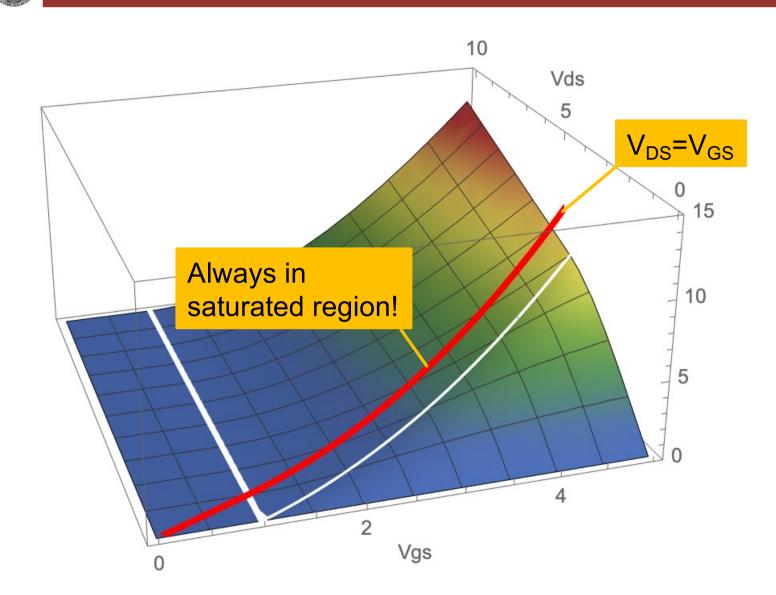

#### The Diode-Connect MOS

Consider a MOS with Drain and Gate connected

V<sub>DS</sub> = V<sub>GS</sub> → V<sub>DS</sub> = V<sub>GS</sub> > V<sub>GS</sub> - V<sub>T</sub> = V<sub>DSat</sub>

$\rightarrow$  A diode connected MOS is always in saturation!

Important:

K/2 VV/L (V<sub>DS</sub>-V<sub>T</sub>)<sup>2</sup> (1+λ V<sub>DS</sub> (in 'strong inversion')

For any current  $I_D$ ,  $V_{GS}$  adjust so that this current can flow!

## Illustration: $V_{DS} = V_{GS}$

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

## THE CURRENT MIRROR

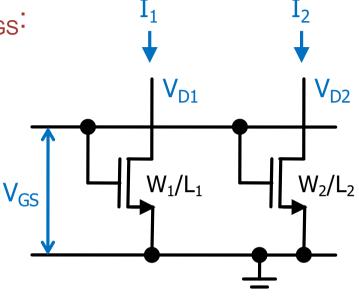

## Transistors with same V<sub>GS</sub>

Consider 2 NMOS with same V<sub>GS</sub>:

#### Assuming saturation:

•  $I_1 = \frac{K}{2} \frac{W_1}{L_1} \left( V_G - V_T \right)^2 \left( 1 + \lambda_1 V_{D1} \right)$  $K W_2$

•

$$I_2 = \frac{K}{2} \frac{W_2}{L_2} \left( V_G - V_T \right)^2 \left( 1 + \lambda_2 V_{D2} \right)$$

•

$$\rightarrow \frac{I_2}{I_1} = \frac{W_2/L_2}{W_1/L_1} \frac{1 + \lambda_2 V_{D2}}{1 + \lambda_1 V_{D1}}$$

• For L<sub>1</sub> = L<sub>2</sub>:

RUPRECHT-KARLS-UNIVERSITÄT

- The ratio of input/output current is roughly given by the ratio of the Ws

- The Early effect leads to a ,small' deviation

- The Early effects cancel if  $V_{D1} = V_{D2}$  (for same  $\lambda$ )

#### RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

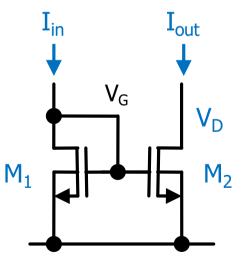

### The Current 'Mirror'

First, we assume that M<sub>1</sub> and M<sub>2</sub> are identical

•

$$W_1 = W_2, L_1 = L_2$$

- Now connect M<sub>1</sub> as a diode

- $V_G$  adjusts such that  $I_{in}$  flows into  $M_1$

- $M_2$  and  $M_1$  have the same gate voltage  $\rightarrow I_{out} = I_{in}$

- The current is 'mirrored' from the input to the output

In more detail, Early Effect must be taken into account

•  $I_{out} = I_{in}$  exactly only for  $V_D = V_G$  (do you understand why?)

#### RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

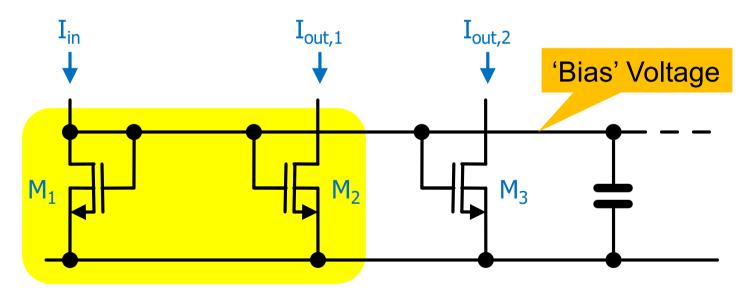

### Varying the Output Current

- If  $W_2 \neq W_1$  (assuming still  $L_1=L_2$ ), then  $I_{out} = W_2/W_1 I_{in}$

- L<sub>1</sub> ≠ L<sub>2</sub> should be avoided because Early Effects (i.e. λs) are different

- Additional MOS can be connected to give further outputs

- The gate voltage of the sources is called a 'Bias' Voltage

- It should be 'decoupled' with capacitors to *the source potential* to be 'stable' and noise free.

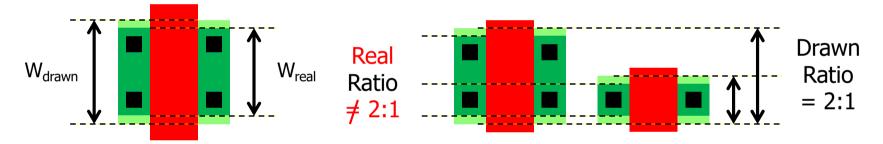

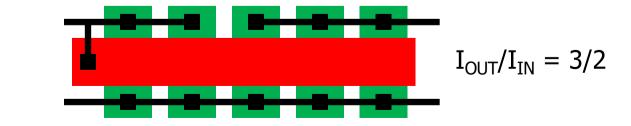

# Large W vs. Multiple MOS

RUPRECHT-KARLS-UNIVERSITÄT

- The ratio W<sub>2</sub>/W<sub>1</sub> is used for current multiplication

- If this is implemented by MOSs with different layouts, edge effects can lead to unknown ratios.

- To be more precise, the real W of a device is often  $W_{real} = W_{drawn} - W_{offset}$  ( $W_{offset}$  can have both signs)

- Real Ratio != Drawn Ratio! → use *multiple identical* devices!

- For a non-integer ratio A/B, use B MOS on diode side and A MOS on output side. (In practice, add 'dummy' devices for matching)

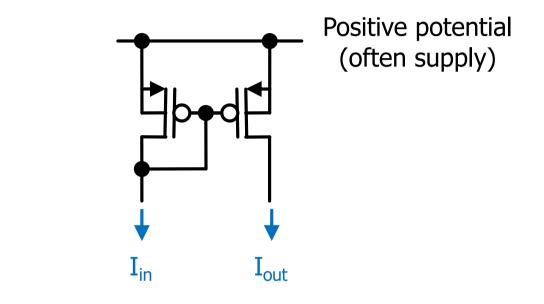

### The PMOS Mirror

Here is how a PMOS mirror looks like:

- Same principle and topology.

- Inverted polarities.

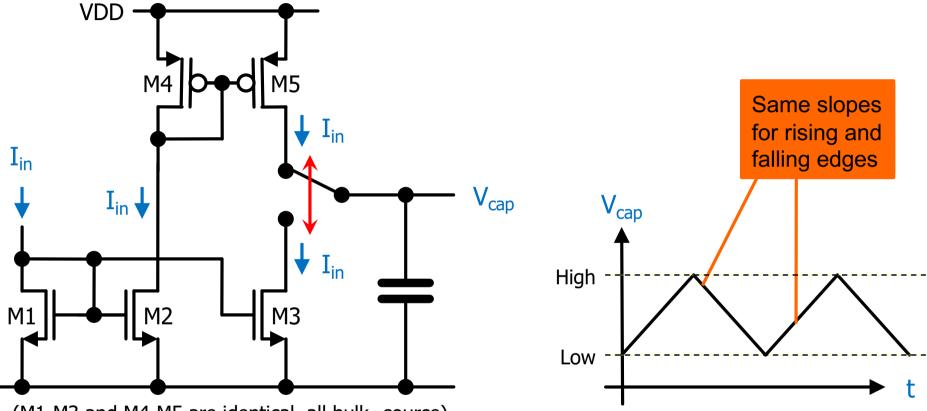

### A Possible Application: Triangular Waveform

#### A capacitor is charged / discharged with same current

(M1-M3 and M4-M5 are identical, all bulk=source)

RUPRECHT-KARLS-UNIVERSITÄT

- Switches: MOS with large W/L controlled by 0/VDD

- Switching could be done by comparing V<sub>cap</sub> to a high- and low- level...

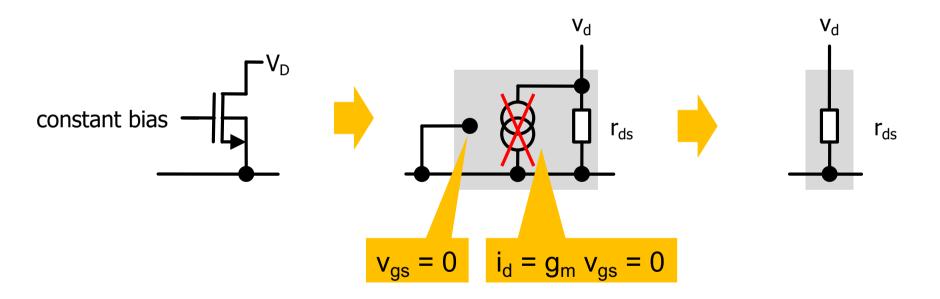

- The Output Resistance r<sub>out</sub> of the Mirror is just that of the (output) MOS

- This is obvious from the small signal model

- The Gate voltage is *constant*, so there is *no small signal*:  $v_{gs} = 0$

r<sub>ds</sub> depends on the current and on the geometry (W,L)

#### UNIVERSITÄT HEIDELBERG

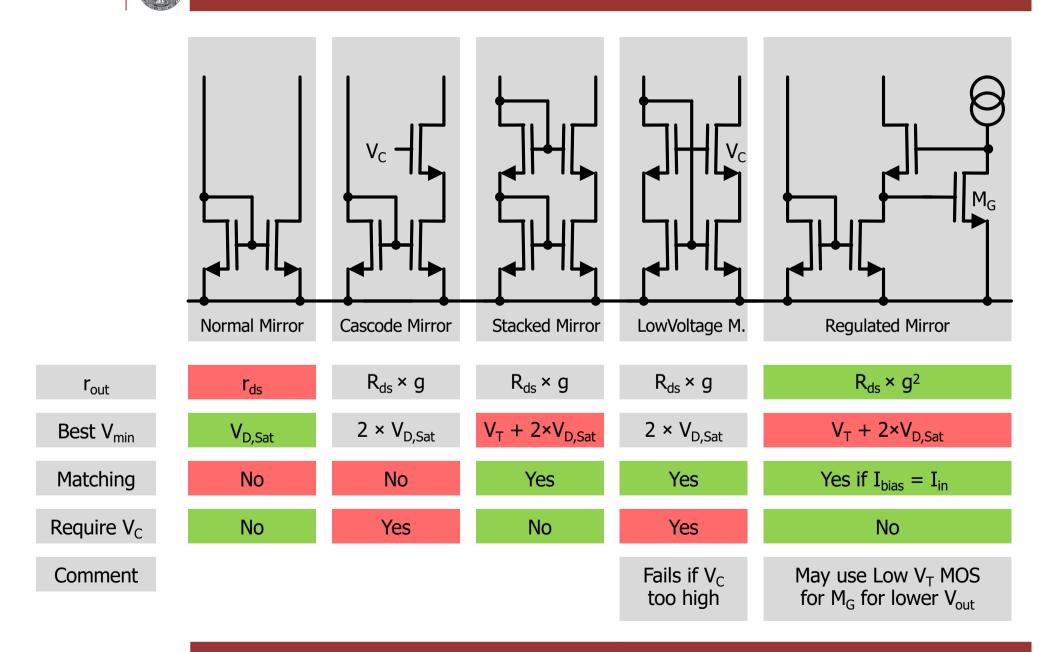

### Good and Bad Mirrors

- Normally, the output MOS of the mirror is used as a *current* source. We therefore want

- high output resistance  $r_{ds} \rightarrow$  we need small  $I_D$ , large L

- low saturation voltage  $\rightarrow$  we need small I<sub>D</sub>, small L, large W

- Therefore: Good mirrors must have large L and W

- large L to increase output resistance

- large W to lower saturation voltage

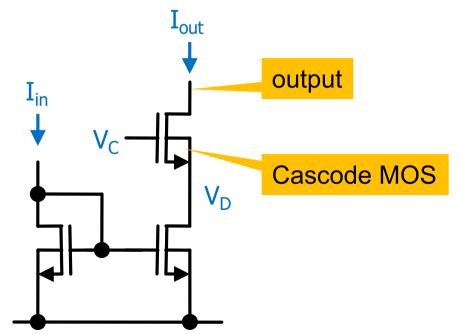

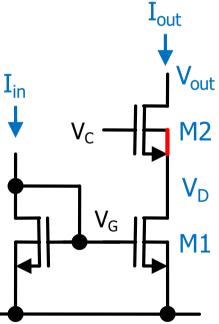

## THE CASCODE

## Improving the Mirror: The Cascode

- The output current in a normal mirror changes, because output voltage = drain voltage

- By inserting another MOS between output and drain, the drain voltage is kept (more) constant

- the output current changes (less)

- the output resistance is higher

- The upper MOS is called a CASCODE (transistor)

RUPRECHT-KARLS-UNIVERSITÄT

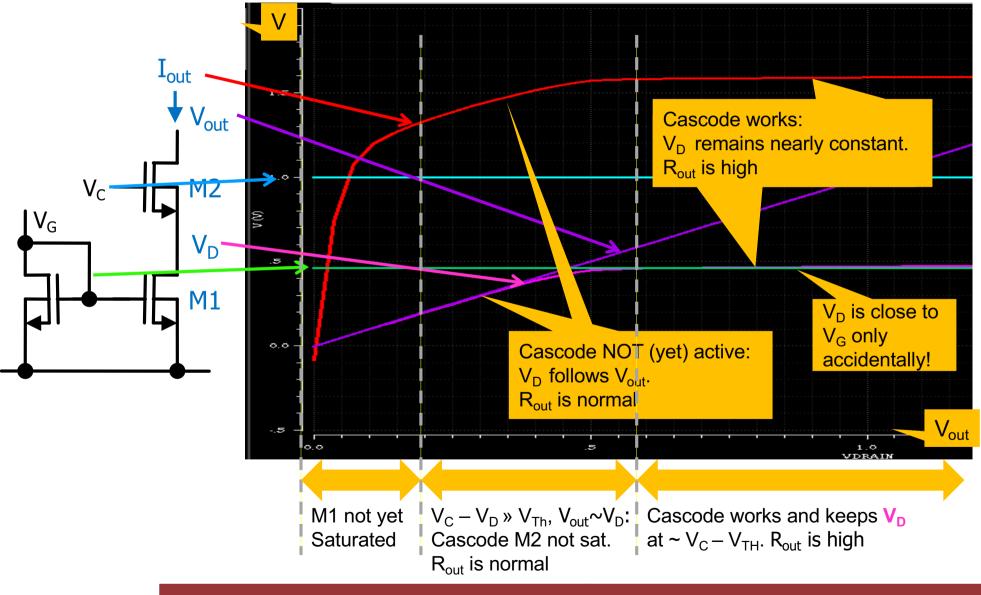

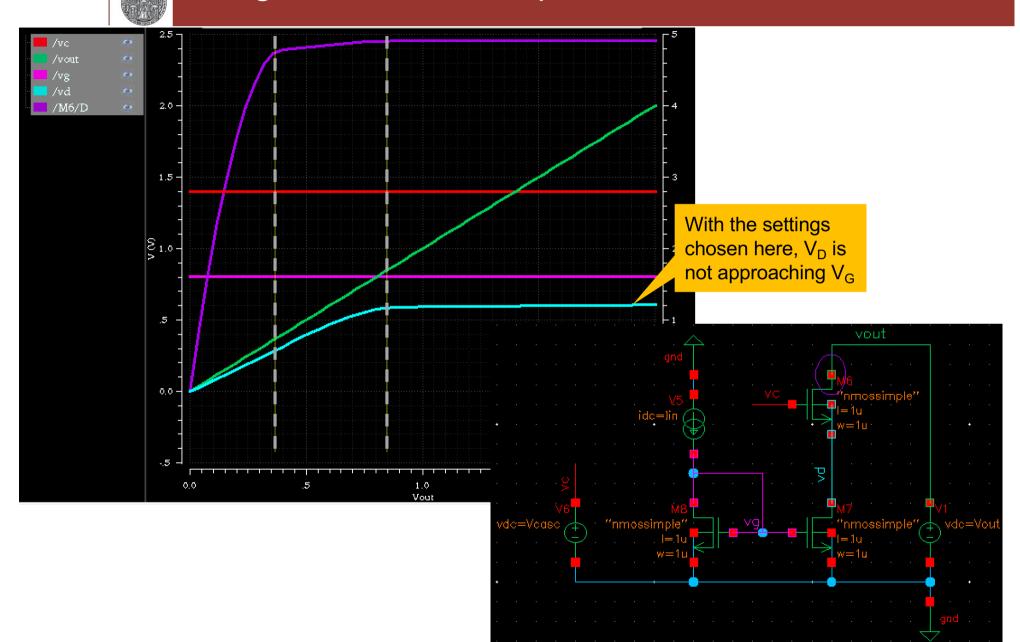

### The Cascoded Current Source in Action

#### Simulation for V<sub>C</sub> = 1V (not optimal, see later...)

RUPRECHT-KARLS-UNIVERSITÄT

#### Using model 'nmossimple' :

RUPRECHT-KARLS-UNIVERSITÄT

### Crucial: Correctly Biasing the Cascode

- The gate voltage of the cascode MOS M2, V<sub>C</sub>, defines the drain voltage V<sub>D</sub> of the 'current setting' MOS M1

- $V_D$  is roughly one threshold voltage below  $V_C$

- More precisely,  $V_D = V_C V_T Sqrt(I_D 2/K L/W)$

- (This holds when Bulk and Source are connected (-), otherwise, the Substrate Effect lowers V<sub>D</sub> even more)

- V<sub>D</sub> (and thus V<sub>C</sub>) should be chosen

- *High enough* to keep M1 'just' saturated

- As low as possible so that  $V_{\text{out}}$  can be low

- The ,total' saturation voltage at the output for optimal choice is ~ *twice* that of M1 (if M1 and M2 have same sizes)

RUPRECHT-KARLS-UNIVERSITÄT

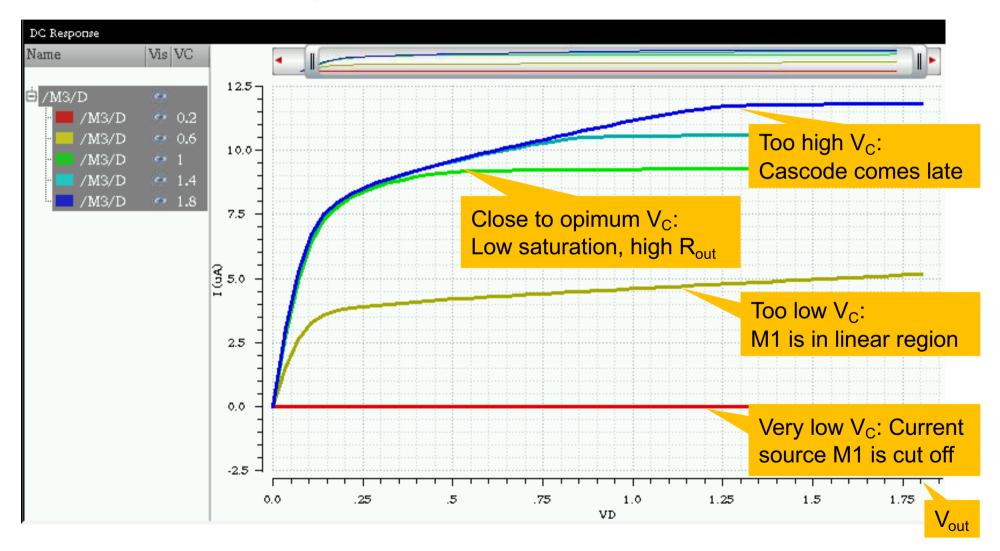

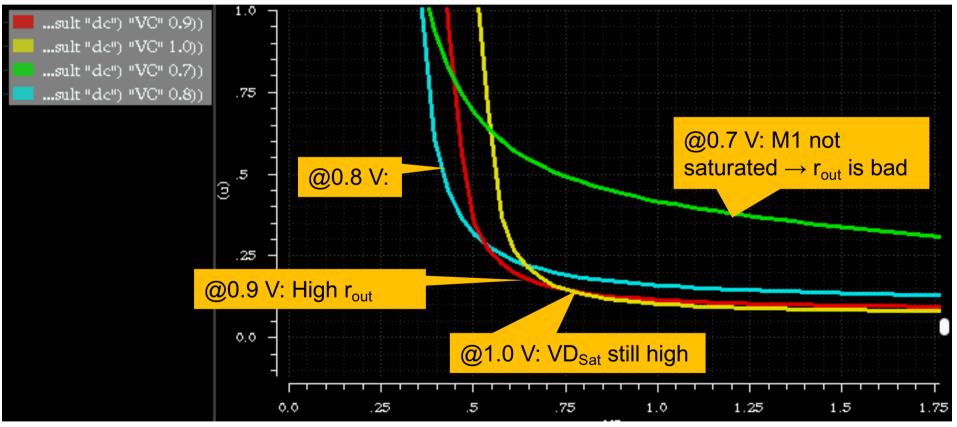

## Simulation: Varying V<sub>C</sub>

#### • Sweep V<sub>C</sub> from 0.2...1.8 V:

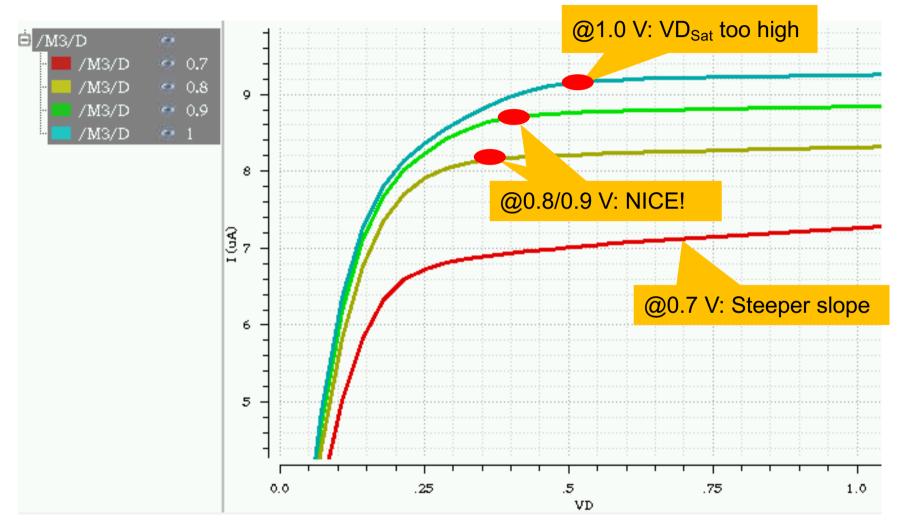

# Zoom of 'Optimum' V<sub>C</sub>:

#### • Sweep 0.7...1.0 V

### Rout and dynamic range in more detail

- Look at derivative of output characteristic ( $\partial I_{out} / \partial V_{out} = 1/r_{out}$ )

- Small is good

- Again, blue (0.8 V) or red (0.9 V) are best...

Note: Do not believe simulations to better than 50-100 mV!

- 0.8 V is too close to 'bad' curve for 0.7 V.  $\rightarrow$  Chose 0.9 V

CCS - Current Mirrors

P. Fischer, ZITI, Uni Heidelberg, Seite 23

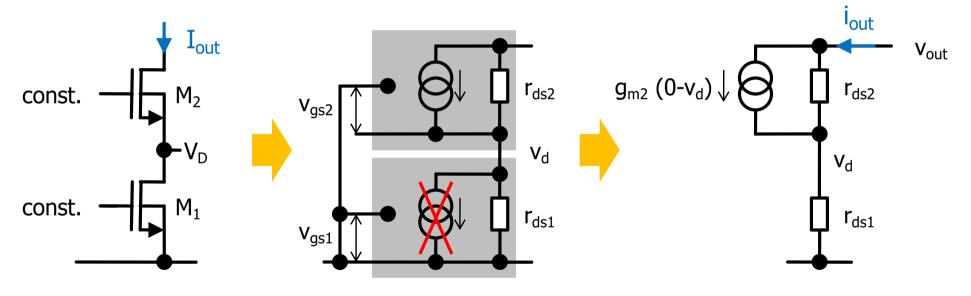

- Small signal analysis

- We only need to consider the output part

- Fixed voltages are equivalent to ground (in small signal!)

- The current source in M1 delivers no current ( $V_{GS}$  = fix)

Current sums:

- $i_{out} = (v_{out} v_d)/r_{ds2} g_{m2} v_d = v_d / r_{ds1} \rightarrow v_d = ... \rightarrow r_{out} = v_{out}/i_{out}$

- $\rightarrow \mathbf{r}_{\text{out}} = \mathbf{r}_{\text{ds1}} + \mathbf{r}_{\text{ds2}} + \mathbf{g}_{\text{m2}} \mathbf{r}_{\text{ds1}} \mathbf{r}_{\text{ds2}} \rightarrow \mathbf{r}_{\text{out}} \cong \mathbf{r}_{\text{ds1}} \times (\mathbf{g}_{\text{m2}} \mathbf{r}_{\text{ds2}})$

CCS - Current Mirrors

© P. Fischer, ZITI, Uni Heidelberg Page24

#### NUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

## (The Calculation)

$$\frac{v_{out} - v_d}{r_{ds2}} - g_{m2}v_d = \frac{v_d}{r_{ds1}} = \mathbf{i}_{out}$$

$$\frac{v_{out}}{r_{ds2}} = \frac{v_d}{r_{ds1}} + \frac{v_d}{r_{ds2}} + g_{m2}v_d$$

$$\frac{1}{v_d} = \frac{r_{ds2}}{v_{out}} \left(\frac{1}{r_{ds1}} + \frac{1}{r_{ds2}} + g_{m2}\right)$$

$$\begin{aligned} r_{out} &= \frac{v_{out}}{i_{out}} = \frac{v_{out}r_{ds1}}{v_d} & \text{i}_{out} = v_d / r_{ds1} \\ &= v_{out}r_{ds1} \frac{r_{ds2}}{v_{out}} \left(\frac{1}{r_{ds1}} + \frac{1}{r_{ds2}} + g_{m2}\right) \\ &= r_{ds2} + r_{ds1} + g_{m2}r_{ds1}r_{ds2} \end{aligned}$$

- The output resistance of a cascoded MOS is a factor of g<sub>m</sub> r<sub>ds</sub> higher than without cascode <sup>(2)</sup>

- g<sub>m</sub> r<sub>ds</sub> is the 'gain' of the Cascode MOS (as we will see...)

- It is typically 30

- The cascode gives a large improvement (in output resistance) for a very 'cheap' cost:

- One more MOS

- Loss of *one* saturation voltage (ideally)

- NO additional power consumption!

- Achieving the same (high) output resistance with a long MOS is very difficult (more space than a second MOS, higher saturation voltage)

#### Cascodes are found in many places!

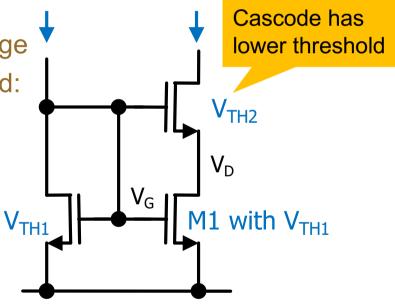

#### A useful cascode trick

- Generating the 'good' cascode voltage is not so easy...

- See exercises

- In some technologies, transistors with *different thresholds* are available.

- This allows the following circuit:

- We use the gate voltage V<sub>G</sub> of the mirror *also* as cascode voltage

- For M1 being saturated, we need:  $V_D > V_G V_{TH1}$

- But  $V_D = V_G V_{TH2} x$ where x depends on current

- The saturation requirement becomes

$$V_G - V_{TH2} - x > V_G - V_{TH1}$$

or

$V_{TH2} < V_{TH1} - x$

With a 'sufficiently low' V<sub>TH2</sub>, this works!

#### UNIVERSITÄT HEIDELBERG

### Summary: The Cascoded Current Source

- A cascode MOS stabilizes the drain voltage of the current source

- The output resistance increases by a factor g<sub>m2</sub> r<sub>ds2</sub>

- This is the 'intrinsic gain' of M2

- It is typically >20 (depending on geometry and current)

- The cascode bias voltage should be chosen such that the current source is *just above* the *edge* of saturation

- The overall saturation voltage of the cascoded source is ~ 2 times the 'unit' saturation voltage

- For advanced circuits, see the exercises!

#### RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

#### **Design Goals for Current Sources**

- High output resistance

- Achieved by large L, cascode, regulation (see exercise)

- Low saturation voltage

- Achieved by large W, optimal biassing

- Matching

- Same Drain voltages (and of course same geometries)

- Speed (sometimes)

- small devices (for small capacitances)

- high current -> large W/L

- But how do we get the input current?

- There are tricky circuits (Bandgap Reference) which can produce voltages / currents which are rather independent of supply voltage, temperature and component parameters!

- See Lecture 'Advanced Analogue Building Blocks'

### Advanced Current Source Circuits

See Exercises

#### Common Current Mirror Topologies