# **Exercise: Thévenin, Resistors, Capacitors**

Prof. Dr. P. Fischer

Lehrstuhl für Schaltungstechnik und Simulation Uni Heidelberg

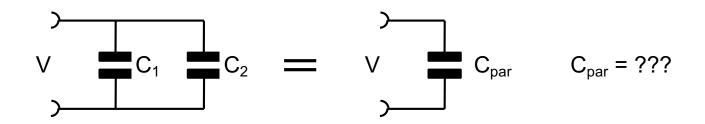

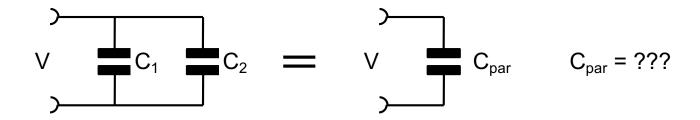

- Derive the expressions for the series and parallel connection of capacitors

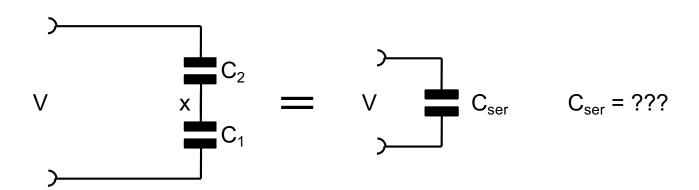

- Use charge conservation (at node x)

1. Charge conservation:

$$V \times C_1 + V \times C_2 = Q_1 + Q_2 = Q_{par} = V \times C_{par} \rightarrow C_1 + C_2 = C_{par}$$

2. Kirchhoff & complex impedance:

$$V sC_1 + V sC_2 = i_1 + i_2 = i_{par} = V sC_{par} \rightarrow C_1 + C_2 = C_{par}$$

### 1. Charge conservation:

Note: no charge can 'escape' the middle node, so that  $Q_1=Q_2=Q_{ser}$   $V = V_1 + V_2 = Q_1/C_1 + Q_2/C_2 = Q/C_1 + Q/C_2 = Q/C_{ser}$  $\rightarrow 1/C_1 + 1/C_2 = 1/C_{ser}$

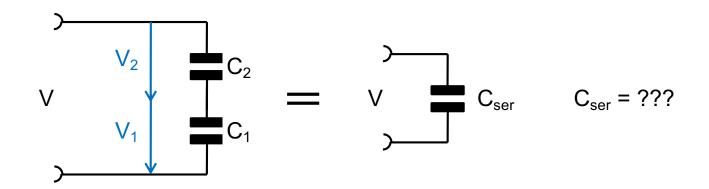

## 2. Kirchhoff & complex impedance:

$$V_1 \, sC_1 = V_2 \, sC_2$$

and  $V_1 + V_2 = V$   $\rightarrow$   $V_1 = V \, C_2 \, / \, (C_1 + C_2)$

$\rightarrow i_1 = V_1 \, sC_1 = V \, s \, C_1 C_2 \, / \, (C_1 + C_2)$

$\rightarrow C_{ser} = i \, / \, (Vs) = i_1 \, / \, (Vs) = C_1 C_2 \, / \, (C_1 + C_2)$

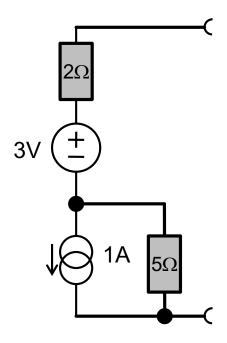

Derive the Thévenin Equivalent for the following circuit:

- Try two different methods:

- Use the Open/Short method with Kirchhoff's rules

- Convert the I-source part to a voltage source first...

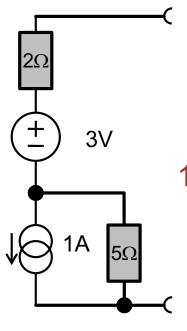

# Solution 2 – Kirchhoff

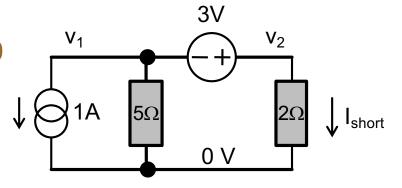

#### 1. Short circuit current:

- EQ1:  $1 A + v_1 / 5\Omega + v_2 / 2\Omega = 0$

- EQ2:  $v_2 = v_1 + 3V$

- $\rightarrow V_2 = -4/7 V$

- $\rightarrow$   $I_{\text{short}} = -2/7 \text{ A}$

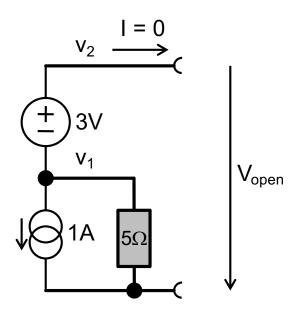

### 1. Open circuit voltage:

- EQ1:  $1 A + v_1 / 5\Omega = 0$

- EQ2:  $v_2 = v_1 + 3V$

•

$$\rightarrow$$

$V_1$  = -5  $V$

•

$$\rightarrow V_2 = V_{open} = -2 V$$

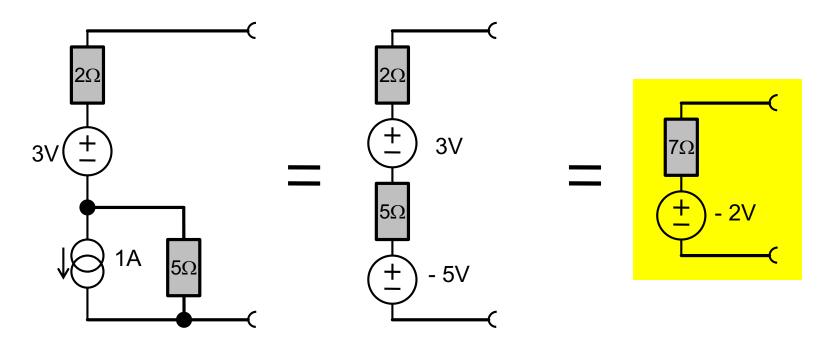

• Source:  $V_0 = V_{open} = -2 \text{ V}$ ,  $R_V = V_0 / I_{short} = 7 \Omega$

# Solution 2 – Thévenin Transformations

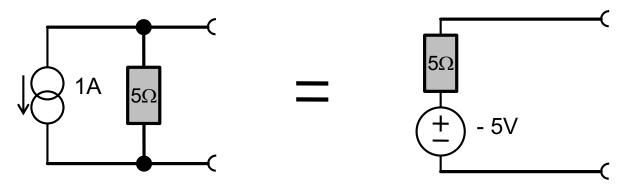

## 1. Convert the current source to a voltage source:

#### 2. Use this in the circuit:

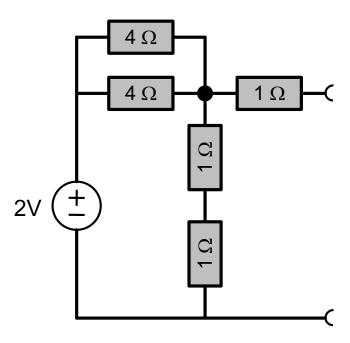

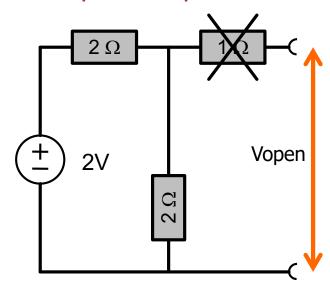

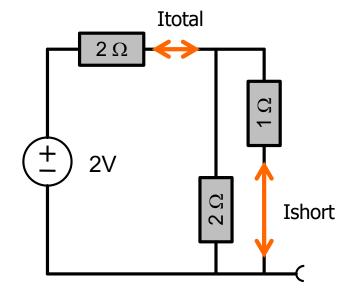

What is the Thévenin Equivalent of the following circuit?

- Use two methods to find the result:

- parallel / series connection of resistors and your knowledge about the voltage divider

- short/open method

■ Parallel-Series Connection, Voltage Divider:

■ Open: Vopen = 1V

#### Short:

Rtotal =

$$2\Omega + 2/3\Omega = 8/3 \Omega$$

Itotal =

$$2V / Rtotal = 3/4 A$$

Ishort =

$$2/3$$

Itotal =  $1/2$  A

Zin = Vopen / Ishort

=

$$1V / \frac{1}{2} A$$

=  $2 \Omega$

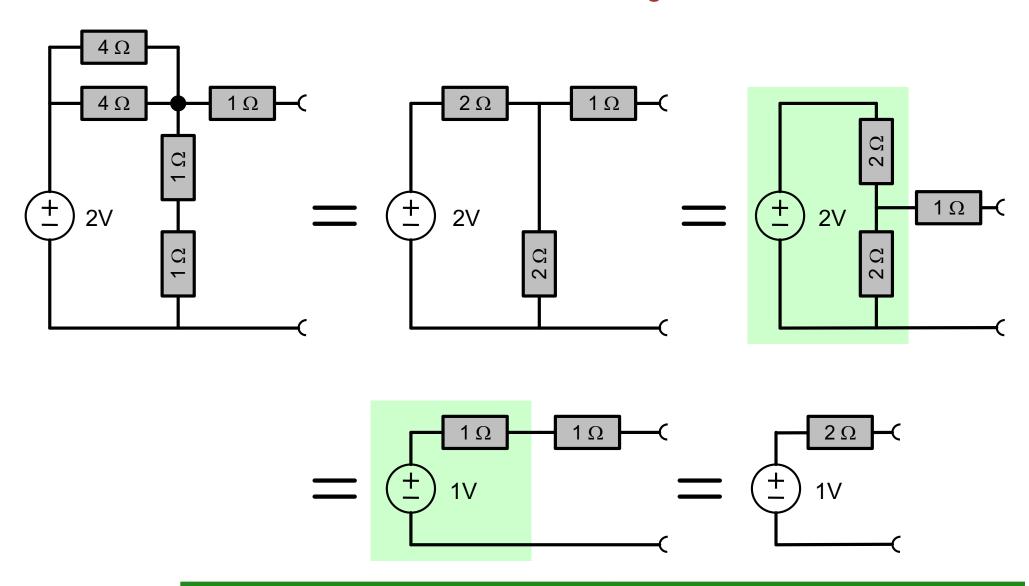

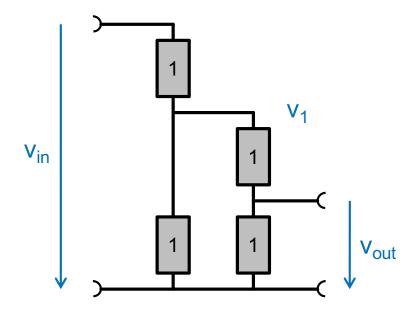

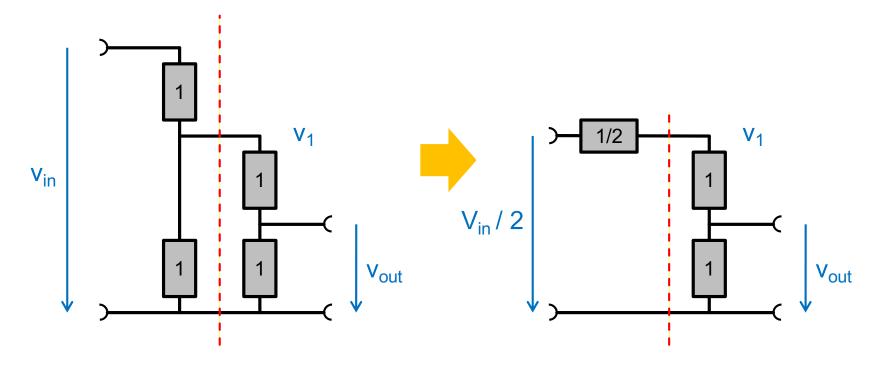

What is the 'gain' (attenuation) of the following voltage divider (all resistors have 1 Ohm):

- Try 3 different methods:

- Your knowledge of parallel / serial connection of resistors

- Kirchhoff's law

- Use your knowledge about the Thévenin equivalent of a voltage divider

- 1. 'By hand':

- The lower part is a *parallel* connection of  $1\Omega$  and  $2\Omega$ . This gives  $(1/1\Omega + 1/2\Omega)^{-1} = 2/3 \Omega$ .

- So we have at node  $v_1$  a voltage divider with  $1\Omega$  and  $2/3\Omega$ . The voltage at  $v_1$  is (2/3) / (1+2/3)  $v_{in} = 2/5$   $v_{in}$

- The voltage at  $v_{out}$  is half of  $v_1$ , so  $v_{out} = 1/5 v_{in}$

#### 2. Kirchhoff

We have current equations at nodes v<sub>1</sub> and v<sub>out</sub>:

$$EQv1 = \frac{vin - v1}{1} = \frac{v1}{1} + \frac{v1 - vout}{1};$$

$$EQvout = \frac{v1 - vout}{1} = \frac{vout}{1};$$

Eliminate[EQv1 && EQvout, v1]

First@Solve[%, vout]

$$\left\{ \text{vout} \rightarrow \frac{\text{vin}}{5} \right\}$$

#### 3. Thévenin:

- The first divider (left of the dotted red line) can be replaced by its Thévenin equivalent of a voltage source with  $v_{in}/2$  and an outputs resistance of  $\frac{1}{2}\Omega$ .

- This creates a divider of 1/2.5 of a voltage  $v_{in}/2$ , so that we get  $v_{in}/5$ .

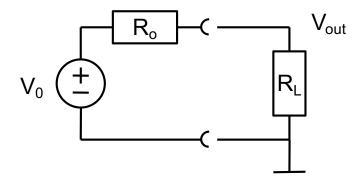

■ A voltage source with voltage V<sub>0</sub> and output resistance R<sub>0</sub> is loaded by a resistor R<sub>L</sub>:

- What is the output voltage V<sub>out</sub>?

- Which current flows in R<sub>L</sub>?

- What power (P = U I) is dissipated in R<sub>L</sub>?

- Check that noting is dissipated for  $R_L=0$  and  $R_L\to\infty$

- For which value of R<sub>I</sub> is the dissipation maximized?

- What is the dissipation?

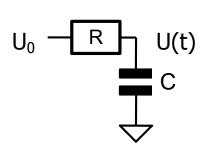

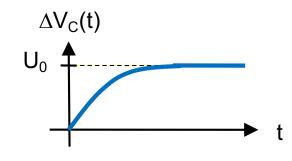

■ We consider charging of a capacitor C though a resistor R to a voltage U<sub>0</sub>.

- $\bullet$  Show that  $\,U(t)=U_0-U_0\,e^{-\frac{t}{RC}}\,\,$  satisfies the differential equation

- Simplify U(t) for small times t<<RC.</p>

- What is the initial slope?

- Derive this slope directly (assuming U(0) = 0).

■ For a capacitor, we have dU/dt = I/C. And we have  $I = (U_0-U)/R$ So the DGL is  $U'(t) = (U_0-U)/RC$

■ The proposed solution  $U(t) = U_0 - U_0 Exp(-t/RC)$  gives The left hand side:  $U'(t) = U_0/RC Exp(-t/RC)$ And the right side:  $U_0 Exp(-t/RC) / RC$ , i.e. the same.

- For small x, the Exp(x) is ~ 1+x, therefore  $U(t) \sim U_0 U_0$  (1-t/RC) = t  $U_0$ /RC

- The slope is derivative of this, i.e U<sub>0</sub>/RC

- This is a charging I/C with an initial current U<sub>0</sub>/R

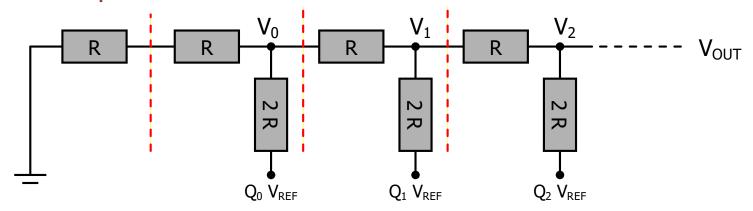

# Exercise 7 (new): R-2R DAC

- Digital-Analog-Converters (DACs) convert a digital (normally binary coded) value into a voltage (or current) which is a normally proportional to the digital value.

- A simple circuit is the R-2R DAC:

- The input voltages at the lower side of the 2R resistors is either 0V or some  $V_{REF}$ , depending of the binary bit ( $Q_0$  is the Least Significant Bit, LSB).

- Show that the output voltage of a R-2R DAC with an arbitrary number N of bits is proportional to Q!

- Hint: Replace the circuit by Thévenin equivalents at the red lines from left to right.

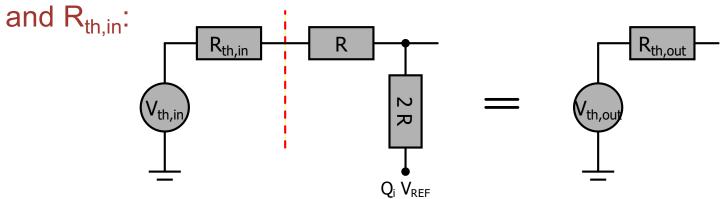

Assume the left (driving) side of a 'red line' is given by V<sub>th,in</sub>

- The output resistance is  $R_{th,out} = (R_{th,in} + R) \parallel 2R$ . For  $R_{th,in} = R$ , we get again  $R_{th,out} = 2R \parallel 2R = R!$ Therefore  $R_{th} = R$  in all stages.

- Therefore,  $R_{th,in}$  and the serial R add up to 2R and we always have a 1:1 divider!:  $V_{th,out}$  is the average of  $V_{th,in}$  and Q  $V_{REF}$

- With  $V_{th,in}$  of the 0-th stage being 0, we get  $V_0 = \text{Average}(0, \, Q_0 \, V_{\text{REF}}) = Q_0 \, / \, 2 \times V_{\text{REF}}$   $V_1 = \text{Average}(Q_0 \, / \, 2 \times V_{\text{REF}} \, / \, 2, \, Q_1 \, V_{\text{REF}}) = (Q_1 \, / \, 2 + Q_0 \, / \, 4) \, V_{\text{REF}}$   $V_2 = \ldots = (Q_2 \, / \, 2 + Q_1 \, / \, 4 + Q_0 \, / \, 8) \, V_{\text{REF}}$  and so on. This is the desired linear relationship.