# SPADIC - Self-triggered readout ASIC for CBM

#### Tim Armbruster, Peter Fischer, Michael Krieger, Ivan Peric

ZITI, Universität Heidelberg michael.krieger@ziti.uni-heidelberg.de

#### DPG Frühjahrstagung Mainz 21.03.2012

A > < = > < =

#### Outline

#### 2 Some details

Michael Krieger SPADIC – Self-triggered readout ASIC for CBM

イロト イ団ト イヨト イヨト

æ

#### Concept

#### SPADIC

Self-triggered Pulse Amplification and Digitization ASIC

- readout of transition radiation detectors at CBM

- used for electron-pion separation (pulse shape)

- oscilloscope-like behaviour: record signal snapshots

- send out messages: signal + metadata

#### Features

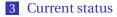

#### 32 channels $(2 \times 16)$

- charge sensitive amplifier + shaper ( $\tau = 80 \text{ ns}$ )

- 9 bit ADC (25 MHz sampling rate, effective res.  $\approx$  8 bit)

- 16 bit digital signal processing (IIR filter)

- hit detection and message building

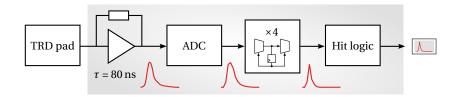

#### each 16 channel group

- time-sorted multiplexing of messages

- special message insertion (epoch markers, buffer overflows, ...)

- 500 Mbit/s serial data link (CBMnet)

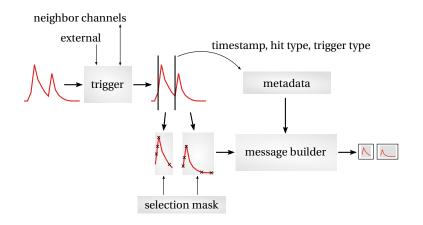

# Block diagram: single channel

伺き イヨト イヨ

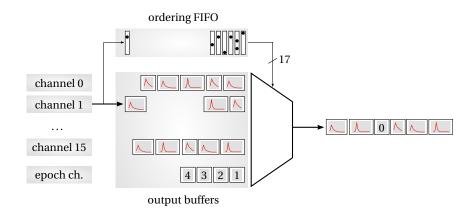

## Block diagram: channel groups

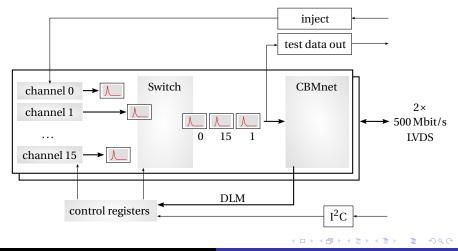

# Signal processing

#### Goal

*Tail cancellation*  $\rightarrow$  reduce pileup  $\rightarrow$  help hit logic

- model signal as sum of exponential terms:  $x_n \propto \sum w_i q_i^n$

- recursion:  $y_n = x_n + bx_{n-1} + ay_{n-1}$

- each filter stage shifts relative weights:  $w'_i = \frac{q_i + b}{q_i - a} w_i$

/╗▶ ◀ ⋽▶ ◀ ⋽

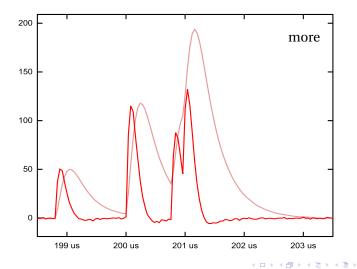

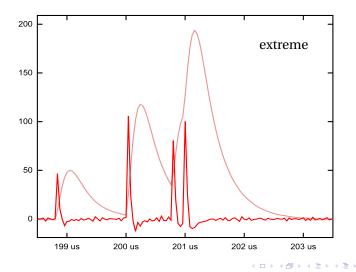

## Signal processing: examples

## Signal processing: examples

æ

## Signal processing: examples

## Hit logic

э

イロト イポト イヨト イヨト

## Ordering mechanism (Switch)

Michael Krieger SPADIC – Self-triggered readout ASIC for CBM

-

Current status

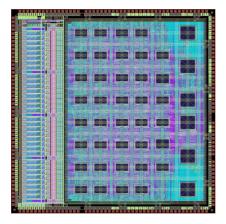

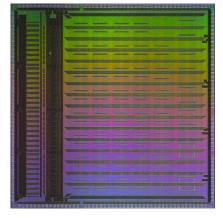

## Layout + Photograph

November 2011

#### February 2012

SPADIC - Self-triggered readout ASIC for CBM

Michael Krieger

イロト イ団ト イヨト イヨト

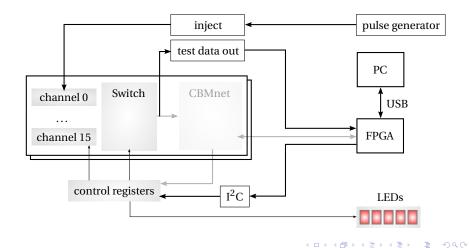

## Test setup (block diagram)

## Test setup (photograph)

## First results

many things already work:

- write register file over  $I^2C \quad \checkmark$

- turn status LEDs on/off :-)  $\checkmark$

- set amplifier/ADC bias voltages (through RF)  $\checkmark$

- get hit messages from channel 0  $\checkmark$

some things need to be done:

- (!) test CBMnet (FPGA firmware not ready)

- find epoch markers (should already be there...)

- test digital filter

- find correct bias voltages/digital configuration

- measure, characterize, write software/documentation, ...

# SPADIC

#### Self triggered Pulse Amplification and Digitization asIC

http://spadic.uni-hd.de