# ASICs for Photon Detection integrating Avalanche Diodes and CMOS Readout

Prof. Dr. Peter Fischer Institute for Computer Engineering (ZITI), Heidelberg University

Fermilab ASIC Department Talk: SPADs for fundamental research

### Content

- What are SiPMs ?

- 2D Single Photon 'Imaging' Test Chips:

- Architecture Details

- Measurement Results

- More Architectures

- Concepts

- Possible Applications

- Some Results

- Please note: Most of the work presented are (not funded) side activities in my group ('academic freedom') and a lot is not yet published.

- Do not spread too much.

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

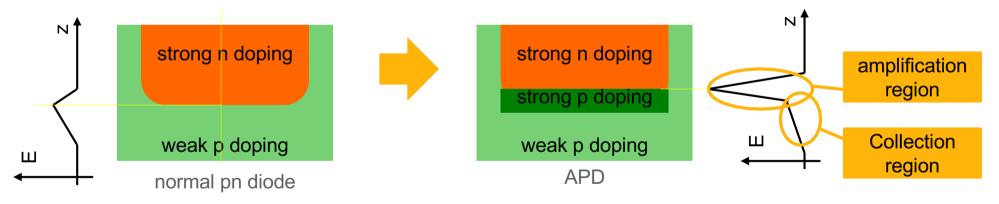

# Single Photon Avalanche Photo Diode (SPAD)

- Goal: Detect a single (optical) photon

- Problem:

- This photon creates only one electron-hole pair when absorbed

- This charge is *very* small and very hard to see *directly* (noise! → must cool...)

- Solution: Amplify the signal in the device

- Create a diode with a very high field in the depletion region (This needs strong doping & a 'high' external voltage, 30-300 V)

- Carriers drift from the depletion=collection region to the amplification region

- They are accelerated by the high field and create secondary ionization

→ an *avalanche* is created, leading to a *large charge* (10<sup>5</sup>-10<sup>6</sup> eh pairs)

- This normally discharges the device so that the fields drop and avalanche stops

UNIVERSITÄT

HEIDELBERG

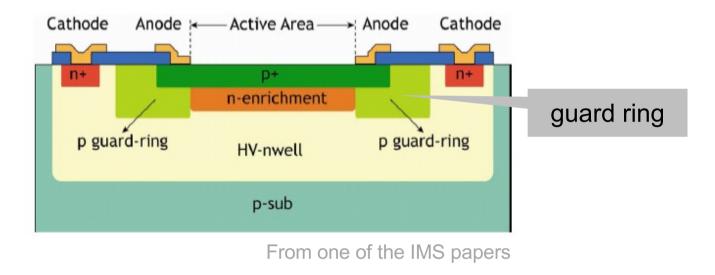

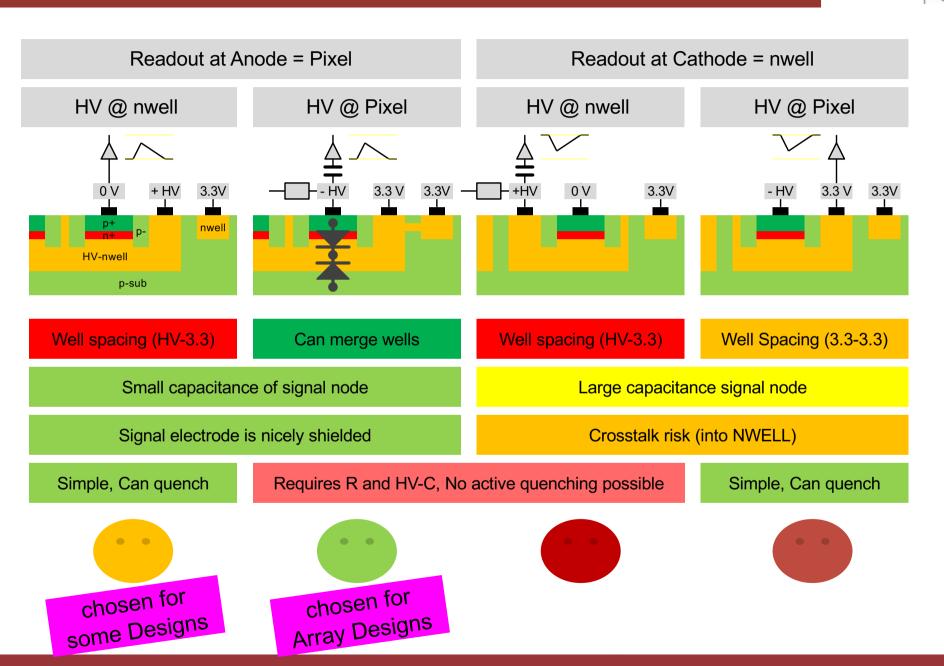

# **Realistic SPAD**

To avoid (too) high fields at the edges (1/r effect), the edge region has lower doping ('guard ring'):

- This leads to some 'dead area' between SPADs

- ~7um in our case

- (In this implementation, the lower SPAD contact (NWELL) is isolated from the p-substrate by a diode)

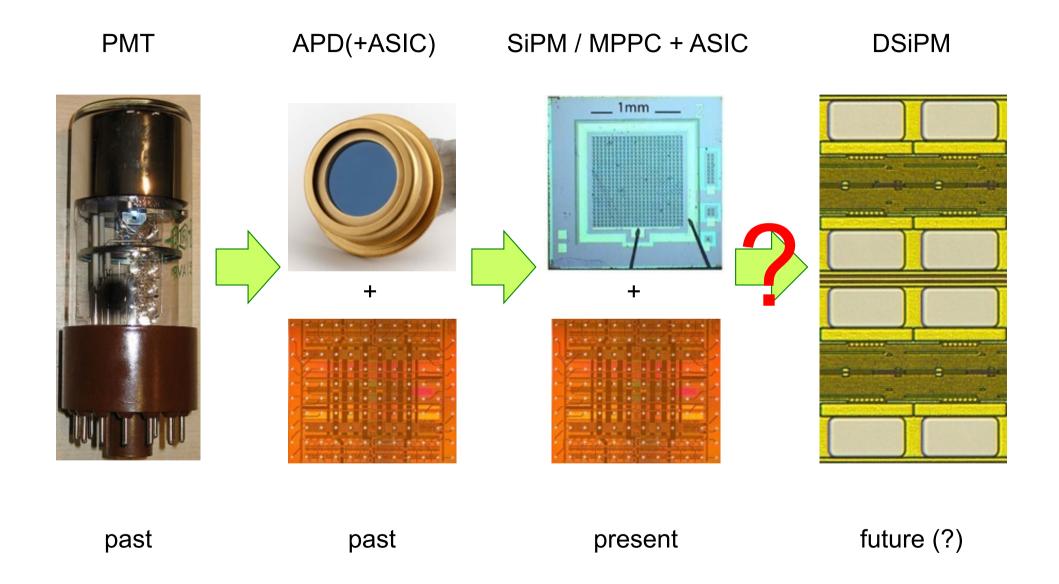

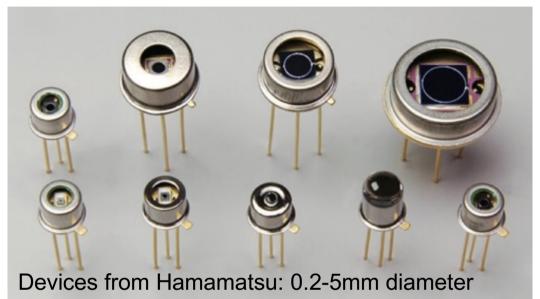

### **Avalanche Photo Diodes**

- A single, large SPAD is an 'Avalanche Photo Diode' (APD)

- Advantages

- Single photon sensitivity

- Large signal (some Volt!)

- Drawbacks:

- The full area is insensitive after a hit until it is recharged (RC, µs!)

- A *single* defect in the area *kills* the full device (large area APDs are very expensive!)

- In the 'high gain' 'Geiger' mode (full breakdown), they deliver only yes/no information, *no amplitude (*i.e. a number of photons)

- In 'linear' amplification mode where amplitude is available gain is lower and HV setting is very delicate

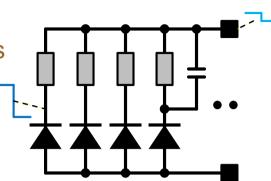

- Solution: 'SiPM'

- Add many SPADs in parallel with separate quench resistors

- Each SPAD (Single Photon APD) works in 'Geiger' mode

- The total signal (charge) is proportional to the number of fired cells, i.e. to the number of detected photons

- (to 'see' the signal immediately, an additional cap. is needed..)

#### Drawback:

- Breakdown of a single SPAD creates a large (voltage) signal 'internally' but only a small fast (voltage) signal 'outside'

- Typical values:

- Cell: (30-50 µm)<sup>2</sup>

- Device: (3-100 mm)<sup>2</sup>

- SPADs: 3.000-100.000

# From SiPM to CMOS SPADs

- SiPMs use ,simple' technology and produce ONLY the SPADs on the chip

- Technology can be optimized for

- low noise (,dark counts') = spurious clicks without any illumination

- high quantum efficiency

- Low optical crosstalk

•

- In nearly all CMOS Technologies, a SPAD structure can be made. But the quality is normally too poor (dark counts)

- Some CMOS vendors do some ,tricks' to improve the SPAD → Can merge ,rather good' SPADs with CMOS electronics

# "CMOS SPADs" or "Digital SiPMs"

# Why CMOS SPADs?

- Advantages (compared to 'SiPM + ASIC')

- Large signal per SPAD (=OV). No Amplifier needed!

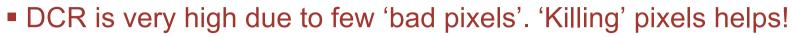

- Can disable individual 'broken' (noisy) SPADs

- Specialized readout architectures possible (incl. integration of TDC, ...)

- Fine granular 2 D position information available

- Simpler mechanics (only one component)

- Lower cost

- Lower power (to be shown...)

### Drawbacks

- Often still higher noise (but can switch off bad SPADs)

- Reduced fill factor (from electronics circuitry)

- Quantum efficiency harder to optimize

- CMOS technology often 'old' (we use 350nm!)

- Limited Density. Must reduce # MOS

- 'Slow'

Fermilab ASIC Department Talk: SPADs for fundamental research

# 2D Imaging Chips

Fermilab ASIC Department Talk: SPADs for fundamental research

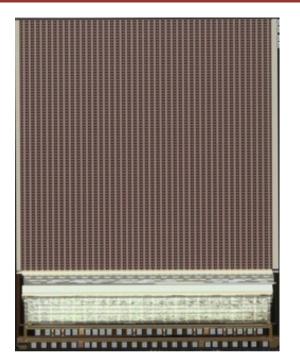

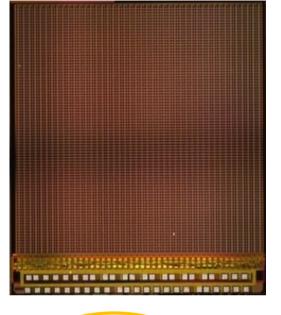

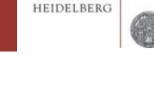

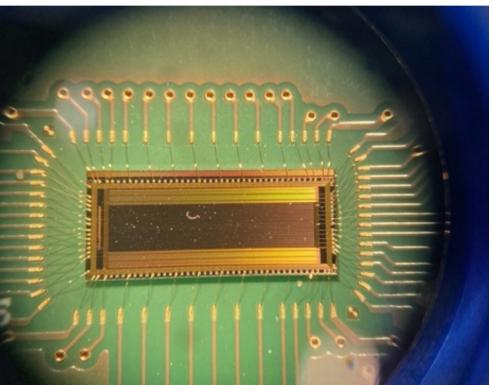

### **Our First Test Chips**

#### IDP1 (2013)

- Chip: 5×7 mm<sup>2</sup>

- 2D array of SPADs

- 88 x 88 pixels

- 38 % fill factor

- full frame readout

- Synthesized digital logic

- Multiplicity output

IDP2 (2014)

- Chip: 5×6 mm<sup>2</sup>

- Improved 2D array

- 55 % fill factor

- faster readout

IDP3 (2016)

- 5×4 mm<sup>2</sup>

- Test structures:

- Array with full frame readout

- Array with fast x-y-readout

- Very compact **TDC**

- Analogue Counter

- Fast SPADs (direct outputs)

- (Design Kit) problem with SPADs!

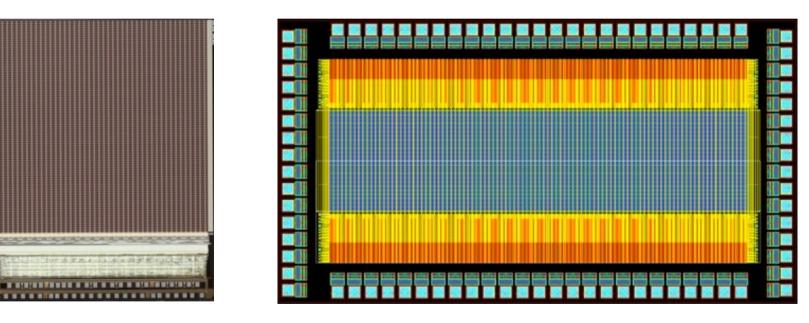

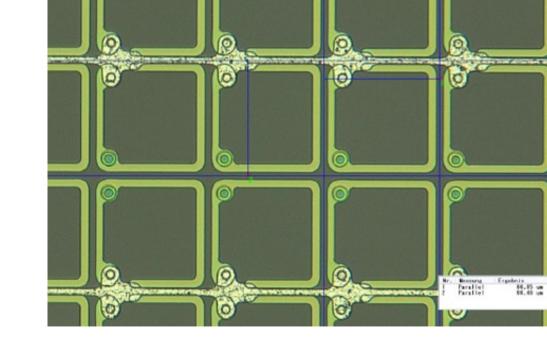

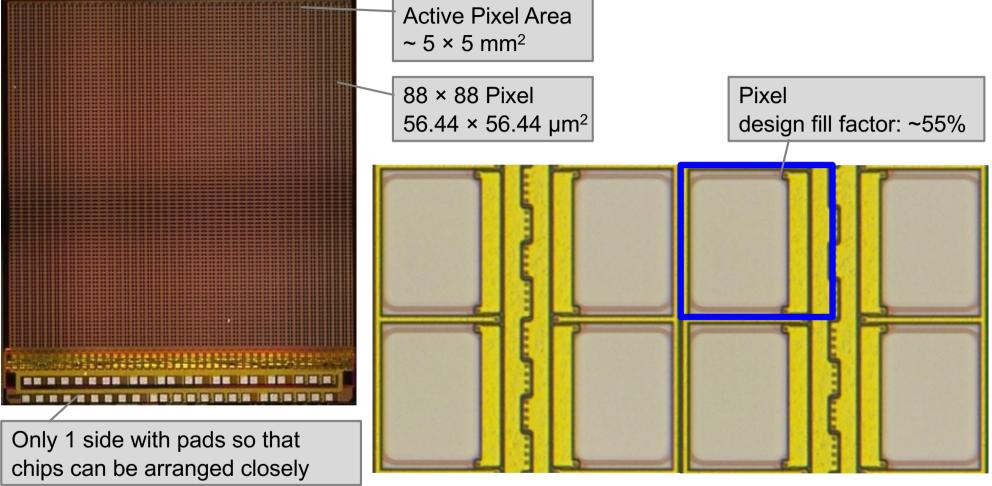

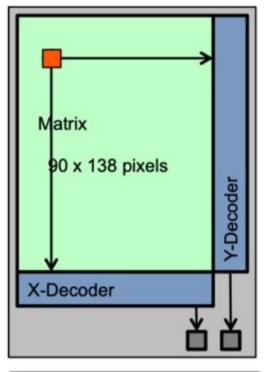

### **IDP2** Chip Geometry

Technology: 0.35 μm 'only' (2 poly, 4 metal levels) @ FhG IMS, Duisburg

#### **Pixel Architecture IDP1**

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

📕 : analog pad 🛛 📘 : digital pad

(slightly simplified schematic)

Fermilab ASIC Department Talk: SPADs for fundamental research

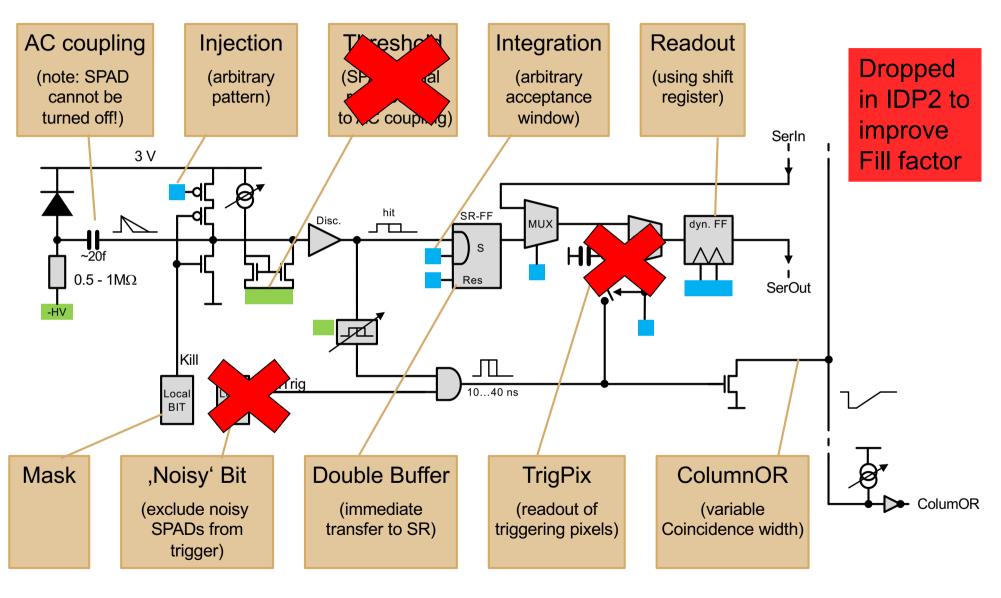

# Layout impressions: Highly Optimized

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

Fermilab ASIC Department Talk: SPADs for fundamental research

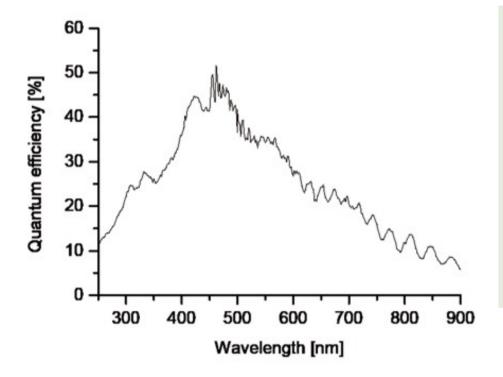

#### Quantum Efficiency

#### As advertised by the manufacturer:

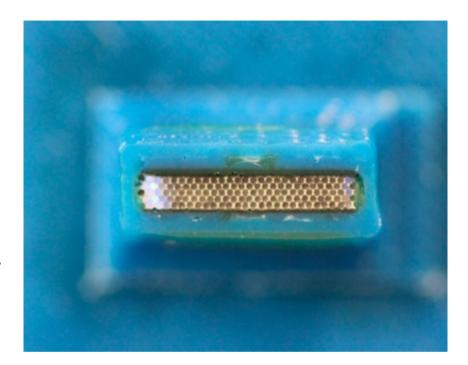

#### Summary of 128 × 2 SPAD-based CMOS line sensor characteristics

| Pixel size (active area)                            | 14 × 76 μm²     |  |

|-----------------------------------------------------|-----------------|--|

| Array size                                          | 2575 × 175 μm²  |  |

| Pixel count                                         | 128 × 2         |  |

| Fill factor                                         | 60 %            |  |

| Measurement period                                  | 2.95 µs         |  |

| Typ. gating width                                   | idth 12.5 ns    |  |

| Breakdown Voltage (V <sub>B</sub> )                 | 27.5 V          |  |

| Temperature dependence of V <sub>Br</sub> 47.7 mV/K |                 |  |

| Typ. operation voltage V <sub>Br</sub> + 2.5 V      |                 |  |

| Crosstalk                                           | 13 %            |  |

| DCR per Pixel (excl. 5% "hot" pixels)               | 327 Hz (133 Hz) |  |

|                                                     |                 |  |

Fermilab ASIC Department Talk: SPADs for fundamental research

# Measurements

Fermilab ASIC Department Talk: SPADs for fundamental research

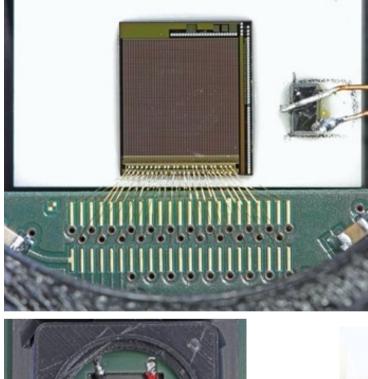

### Mechanics & Cooling

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

- Peltier Cooling (control in FPGA / ARM)

- Local light tight enclosure

Fermilab ASIC Department Talk: SPADs for fundamental research

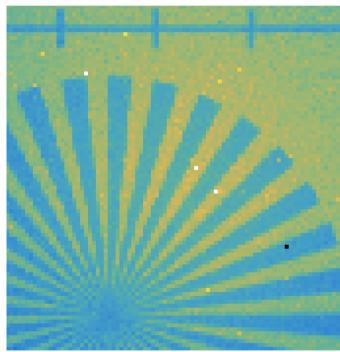

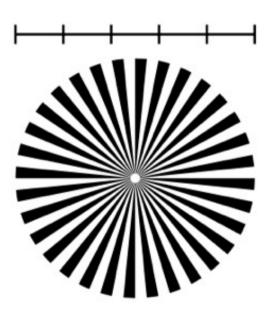

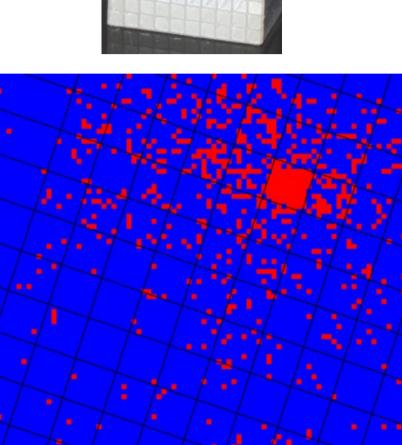

# Proof of principle: Single Photon Imaging

- Build a single photon camera by adding a lens

- Siemens-Stern' of 3 cm diameter imaged in 1m distance in 'full darkness'

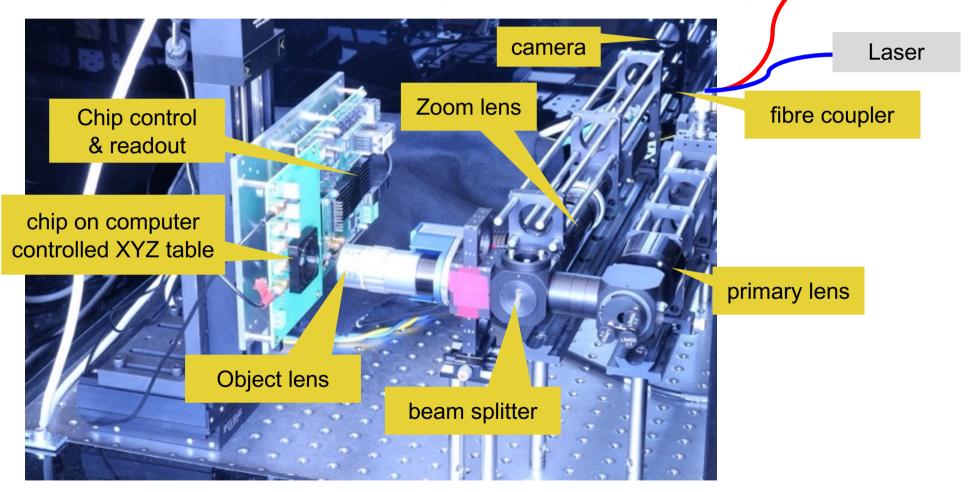

#### Laser Setup

Laser

- Microscope setup can focus a laser on a <5 µm spot</p>

- 'normal' pulsed laser: 642 nm

- fast laser: PiLas PIL040X, 405 nm, (pulse width FWHM < 45ps)

Fermilab ASIC Department Talk: SPADs for fundamental research

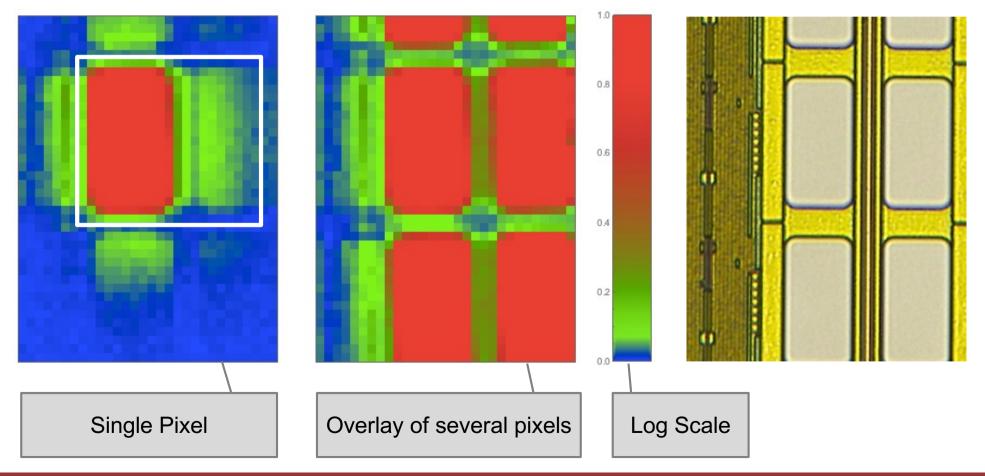

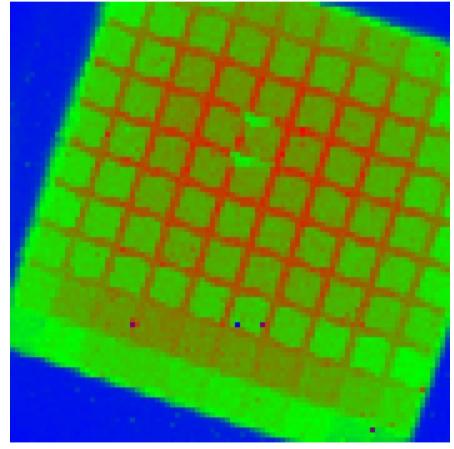

### Laser Scan: 2D Response (IDP1)

- UNIVERSITÄT HEIDELBERG

- Scan over region of 1.5 × 2.0 pixels in 30 × 40 steps (~ 2.8 μm / Step)

- Plot # hits in one pixel for 3000 laser shots (~ 4V overvoltage, I<sub>SPAD</sub> ~6µA)

- Notes: still need to calibrate x-y-steps better & run @ lower intensitiy.

- Design Fill factors are confirmed

Fermilab ASIC Department Talk: SPADs for fundamental research

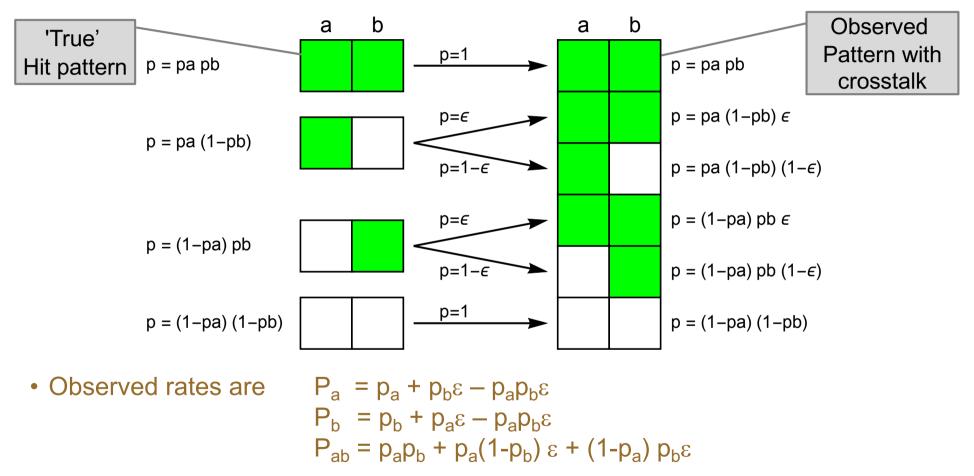

# Crosstalk Determination using Dark Count Events

- Crosstalk leads to higher coincidence rates in (neighbouring) pixel pairs

- Consider dark rates  $p_a$ ,  $p_b$  in pixels a, b and crosstalk probability  $\epsilon$  (a  $\rightarrow$  b, b  $\rightarrow$  a)

• For any pair (a,b), we can measure  $P_a$ ,  $P_b$ ,  $P_{ab}$  and calculate back  $p_a$ ,  $p_b$  and  $\epsilon$

NIVERSITÄT

HEIDELBERG

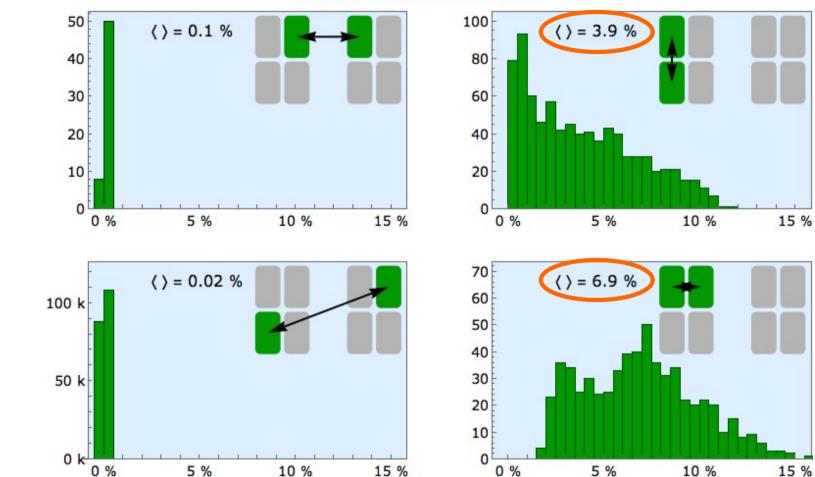

# Measurement for Different Pair Topologies

UNIVERSITÄT HEIDELBERG

Extracted Crosstalk Probabilities

100k events, Only pairs with more Than 20 coincidences are shown

- Crosstalk higher for 'wide' neighbour side, as expected

- Crosstalk is a few precents. Similar results are obtained with our laser

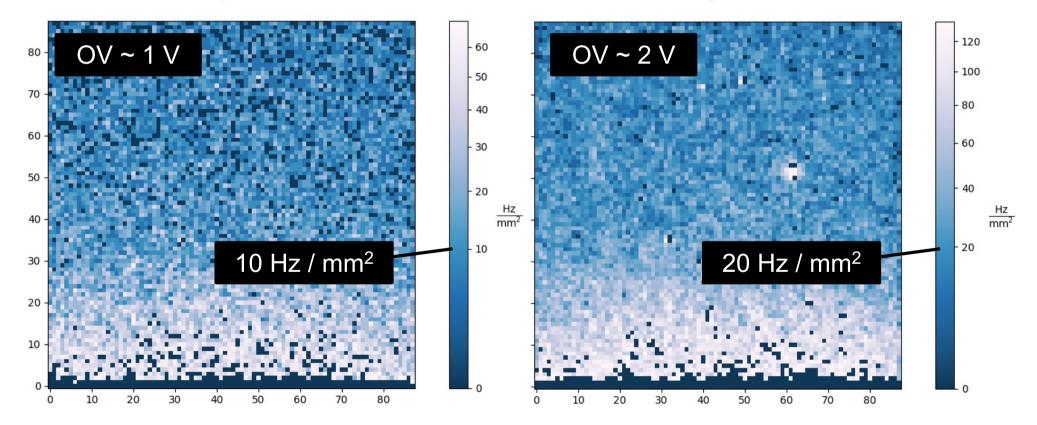

# DCR at Various Overvoltages @ Room Temperature

- Overvoltage = OV = 4,5,6,7 V, Measured @ ~20°C (DCR is lower when cold)

- DCR is referred to active SPAD area

Fermilab ASIC Department Talk: SPADs for fundamental research

NIVERSITÄT

HEIDELBERG

# Cold Operation of IDP2 (in Liquid Nitrogen)

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

Fermilab ASIC Department Talk: SPADs for fundamental research

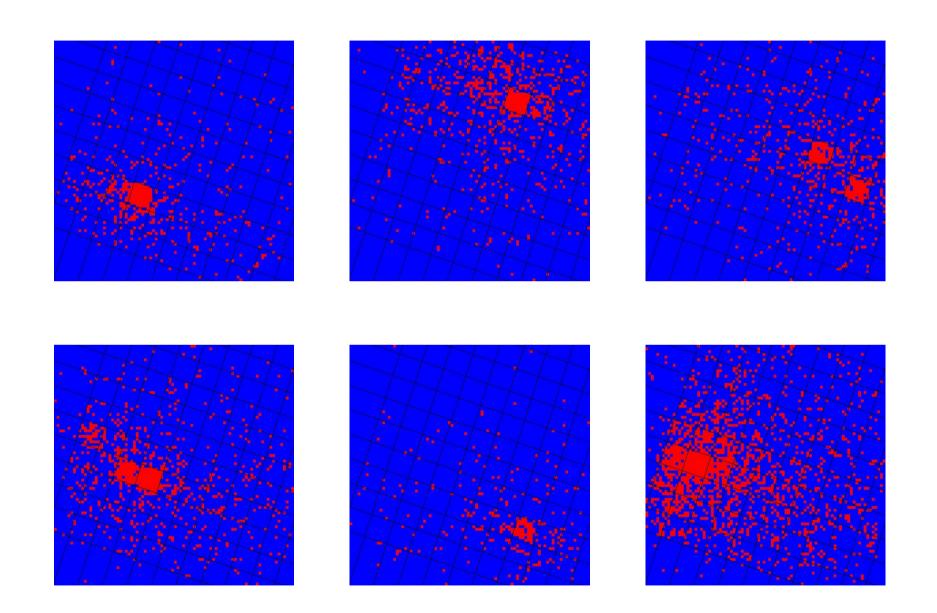

# Dark Count Rate @ LN (5% pixels killed)

#### Very encouraging result: DCR only ~10 Hz/mm<sup>2</sup>

Darkcountrate per area at 22.0V

Darkcountrate per area at 23.0V

# Edge Effect

- We have *much* more DCR at the bottom, close to the electronics

- Unlikely: Temperature effect (chip is immersed in LN!)

- Confirmed: Photon emission from circuit activity in peripheral electronics!!

- Readout architectures for very low DCR must be 'quit'

Darkcountrate per area at 23.4V

Fermilab ASIC Department Talk: SPADs for fundamental research

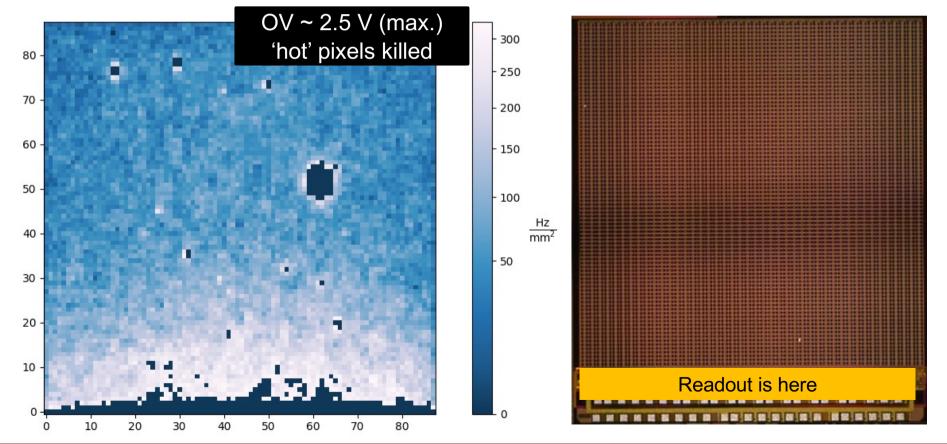

# Application: Study of Scintillator Arrays

- LYSO crystal arrays, 65µm thick ESR reflectors, 10mm height

- Target application: PET

Fermilab ASIC Department Talk: SPADs for fundamental research

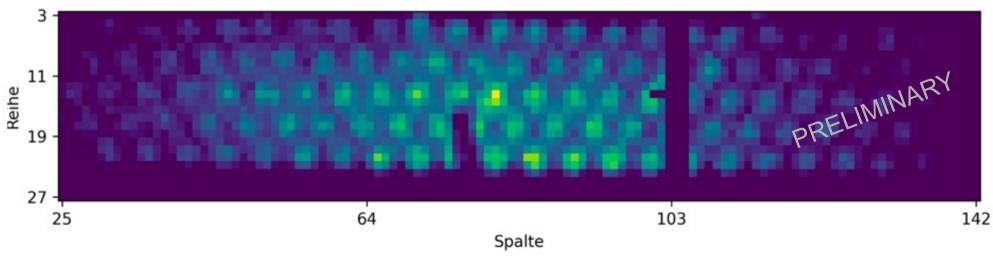

# LYSO Arrays with 0.48 mm pitch (!)

- Measured at ~30°C, OV = 3 V

- Trigger on Mult  $\geq$  4, 200 ns integration

Overlay of 20k events

UNIVERSITÄT HEIDELBERG

Single events

# Many Events Classes

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

# 0

# Engineering Run: More Architectures

Fermilab ASIC Department Talk: SPADs for fundamental research

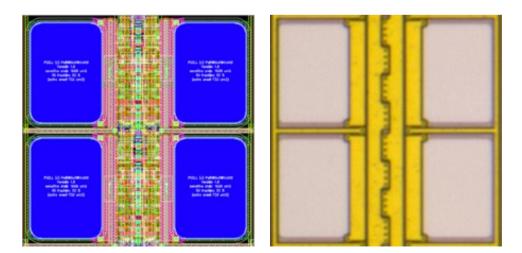

# **Engineering Run**

- Submitted 10/2019

- Back 6/2020

- Reticle ~20x20mm<sup>2</sup>

- 9 different chips

- 5 different architectures

| SCI42                                                        | <b>TCPC</b>   | <b>TEST</b> |

|--------------------------------------------------------------|---------------|-------------|

| 9700 x 3000                                                  | 5700 x 3000   | 3800 × 3000 |

| <b>XYLarge</b>                                               | <b>DARWIN</b> | XYSmall     |

| 9700                                                         | 5700          | 3800        |

| ×                                                            | x             | X           |

| 6100                                                         | 6100          | 6100        |

| IDP4                                                         | <b>TDC</b>    | SCI56       |

| 9700                                                         | 5700          | 3800        |

| ×                                                            | x             | ×           |

| 9700                                                         | 9700          | 9700        |

| sed area is 19500 x 19100 Max. reticle size is 19700 x 19160 |               |             |

Used area is 19500 x 19100

Max. reticle size is 19700 x 19160 Scribe line width has been guessed to 100

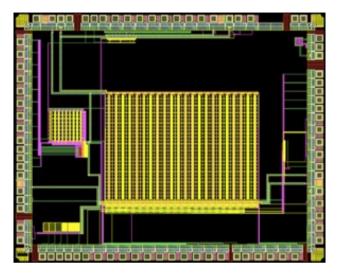

# 1: IDP4: 2D Imaging

- Similar to previous 2D imaging chips

- Improved & faster readout

- Improved 'fast multiplicity logic' to trigger on multiple hits

- Larger: 176 x 166 pixels of 54x54  $\mu m^2$

- 52% fill factor

- Applications:

- 'Camera' >300.000 fps

- Scintillator readout

- Direct particle detection (?)

# 2: XY Readout: Continuous Time Information

UNIVERSITÄT HEIDELBERG

- Single SPAD hit produces X- and Y address

- Error signal generated if >1 SPAD is hit (Such cases 'only' introduce some dead time)

- Time / Hit ~20ns  $\rightarrow$  50 MHz on array

- Provides arrival time for each photon!

- 64% Fill factor

- Applications:

- Fluorescence imaging

- Particle Tracking (?)

- Imaging @ low light

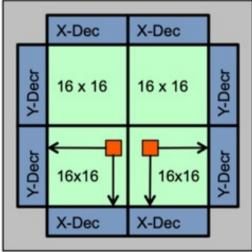

- Two Chip versions:

- Large Chip

- Small chip with 4 quadrants for reduced losses

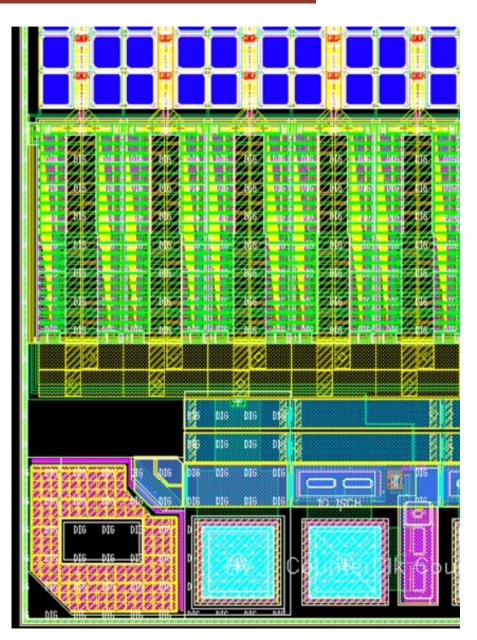

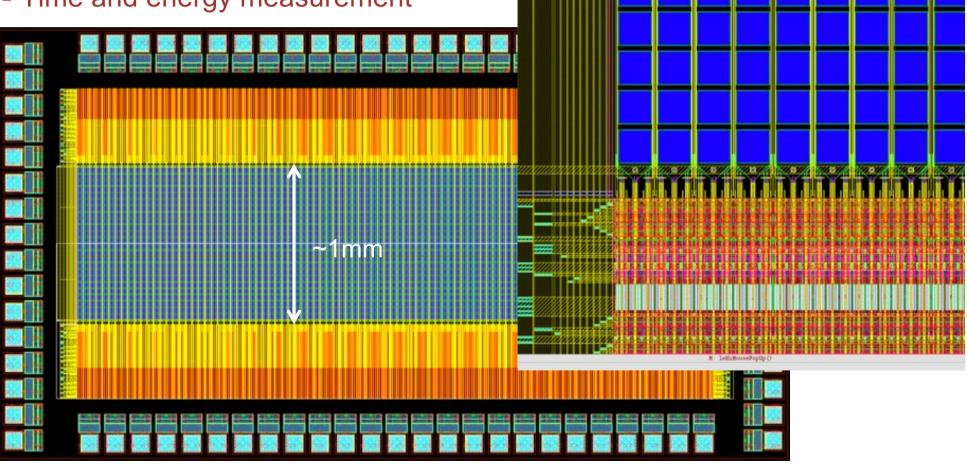

# 3: In-Pixel TDC: Full Frame Timing (ToF Imaging)

UNIVERSITÄT HEIDELBERG

- Every pixel contains a simple Time-Digital-Converter (TDC)

- Hit converts time  $\rightarrow$  voltage (fast ramp)

- Readout digitizes voltage (slow ramp)

- TDC tested to reach <100ps resolution</li>

- Zero suppressed readout

- Operation in 'shots'

- e.g. triggering a laser

- Applications:

- Time-of-Flight Cameras

- Fluorescence imaging with higher multiplicities than xy-readout

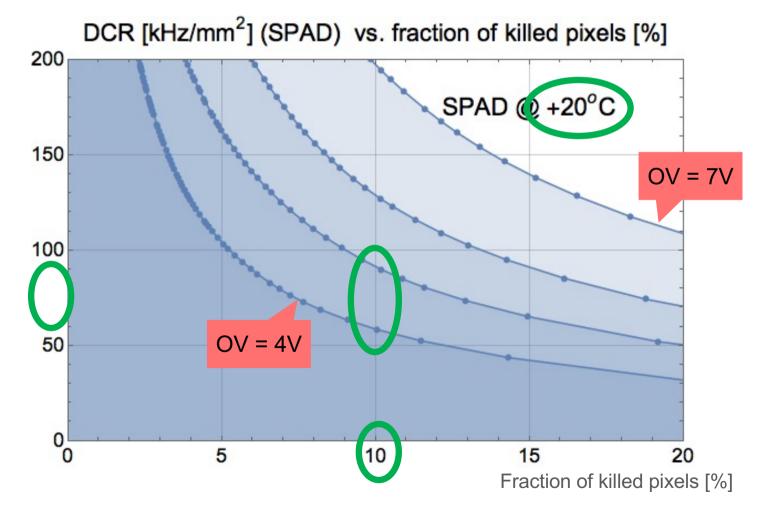

- Designed by PhD student M. Keller

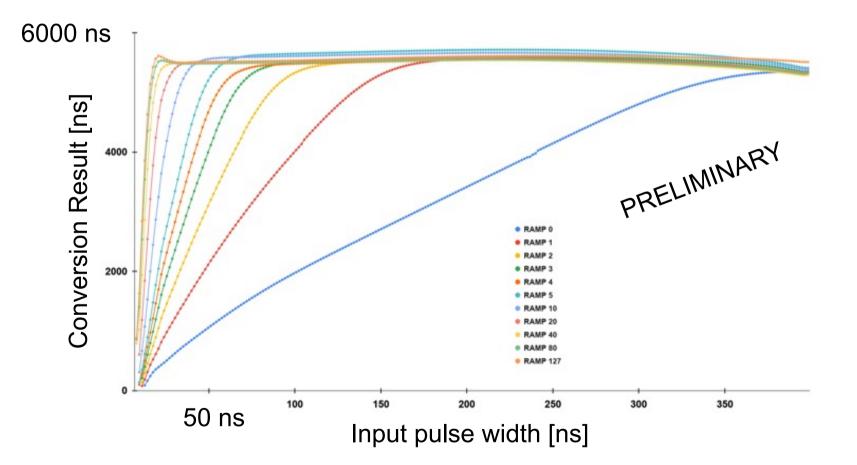

# 3: TDC Chip: Full Scale (Time) Range

UNIVERSITÄT HEIDELBERG

Max. input pulse duration (=FSR) can be varied in very wide range

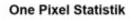

# 3: TDC Chip: TDC Resolution

- So far only testes with electronic injection:

- Inject fixed interval, measure TDC result, calculate sigma

- For ~10ns Full Scale Range, time resolution is  $\sigma$  = 20-50 ps (!)

- Too good to be true ? (350 nm technology!)

# 4: Low Light Detection: Low Power Readout

UNIVERSITÄT HEIDELBERG

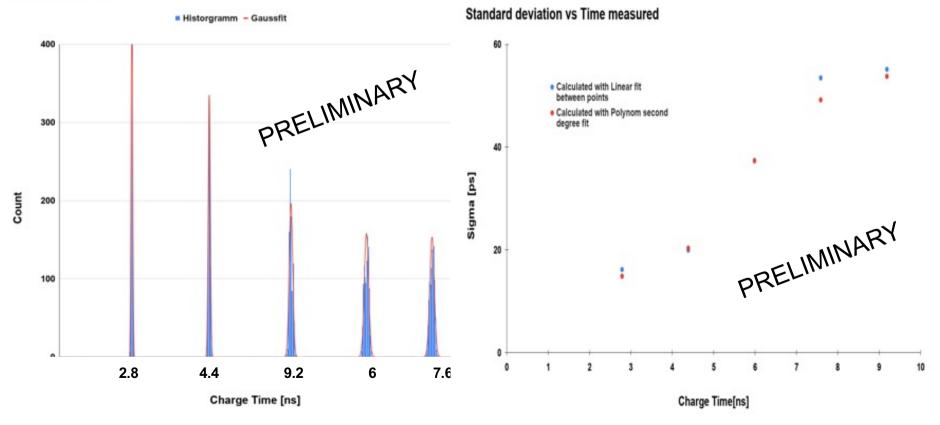

- Many physics experiments search for rare events (proton decay, dark matter) by observing light pulses from a tank filled with a *scintillator*

- In case of DARWIN, scintillator is liquid Xenon (@165K), other experiments use liquid Argon (@87K)

- Present PMT Readout may be replaced by SiPMs or CMOS-SPADs

- Require

- High fill factor

- High quantum efficiency (deep UV...)

- Very low dark count rates (@165K)

- Low power readout (in liquid Xe)

- Low cost to cover large areas (many m<sup>2</sup>)

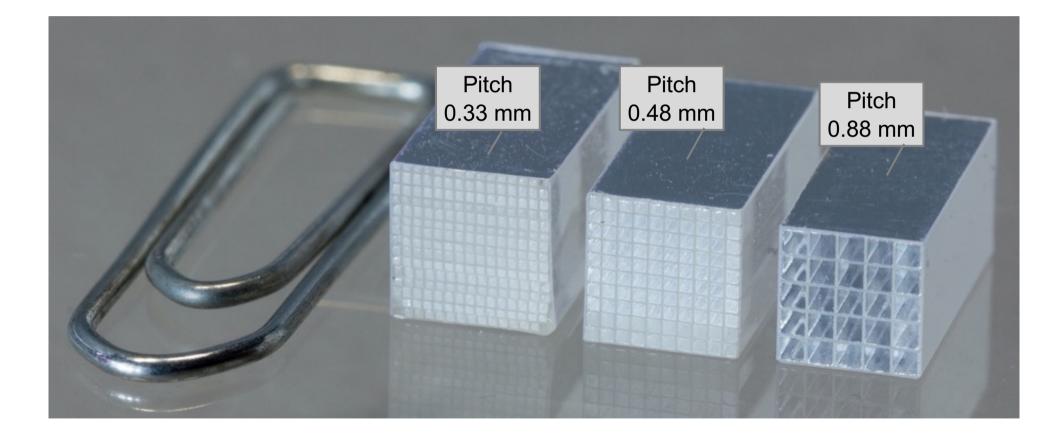

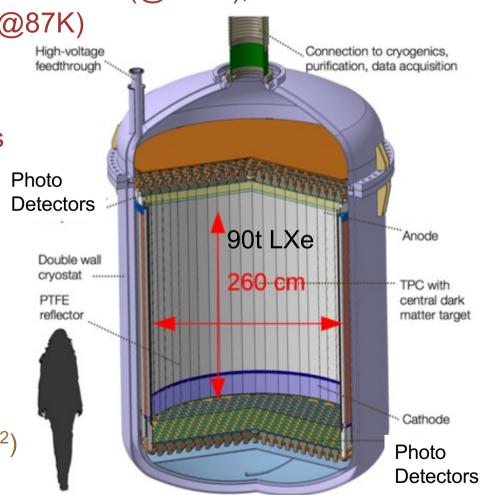

# 4: 'Darwin' Test Chip

- Pixels are grouped to one 'Macro Pixel' of (290µm)<sup>2</sup>

- Group has one XY address

- 10 pixels have different shapes for test

- Each pixel can be disabled ('masked') if noisy

- Test chip has 19x19 Macro Pixels

Designed by PhD student M. Keller

JNIVERSITÄT

HEIDELBERG

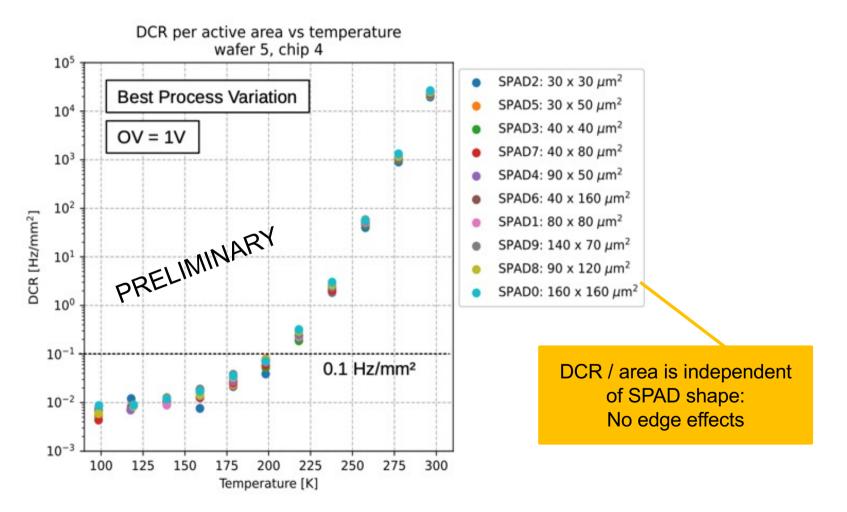

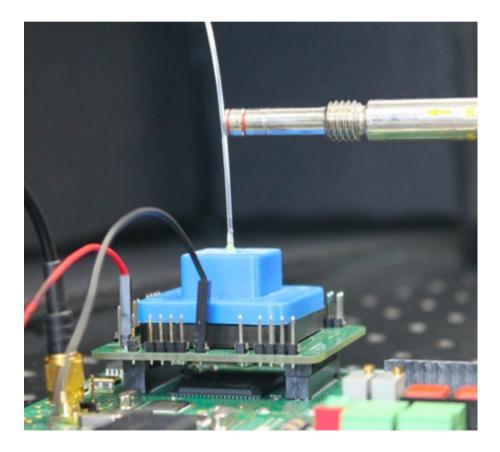

# 4: Darwin Chip

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

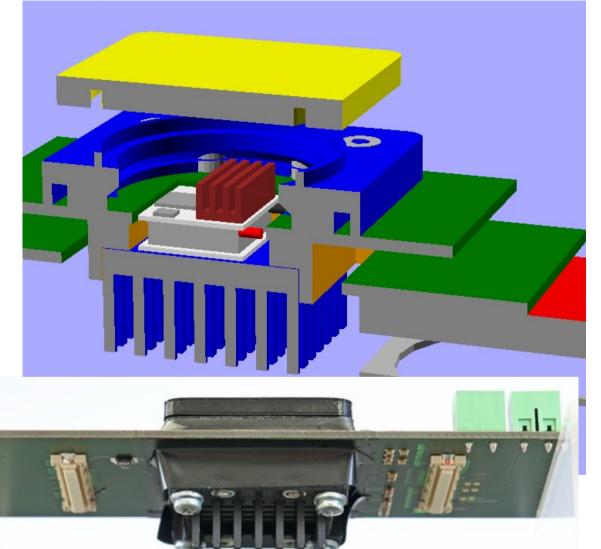

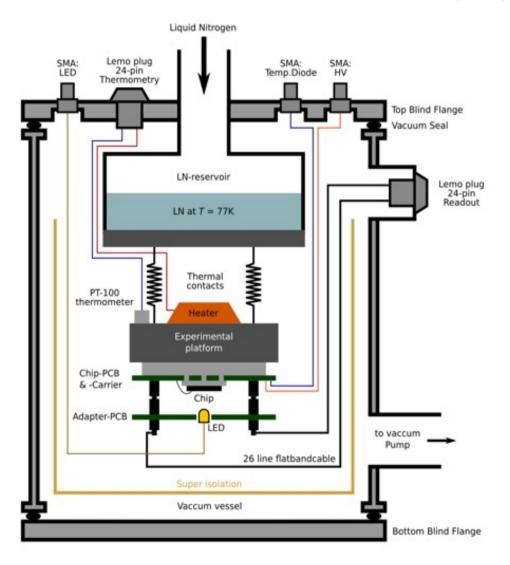

#### Cold Measurements now with fancy cryostat

Fermilab ASIC Department Talk: SPADs for fundamental research

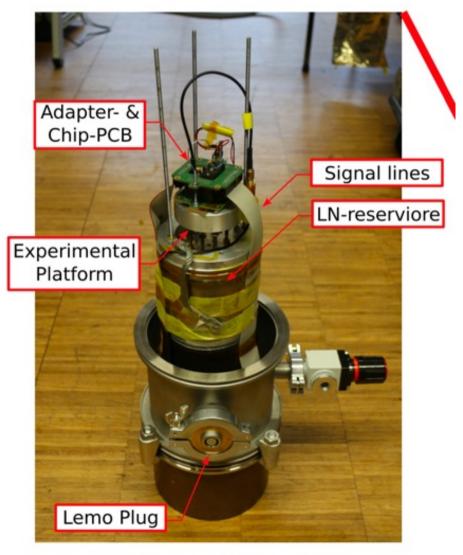

## 4: Darwin: DCR vs Temperature

- DCR in Cold has been improved by manufacturer by technology changes

- Reduce field strengths to reduce 'band-to-band-tunneling' probability

- VERY low DCR of ~0.1 Hz/mm<sup>2</sup> @ 200K down to 0.01 Hz/mm<sup>2</sup> @150K

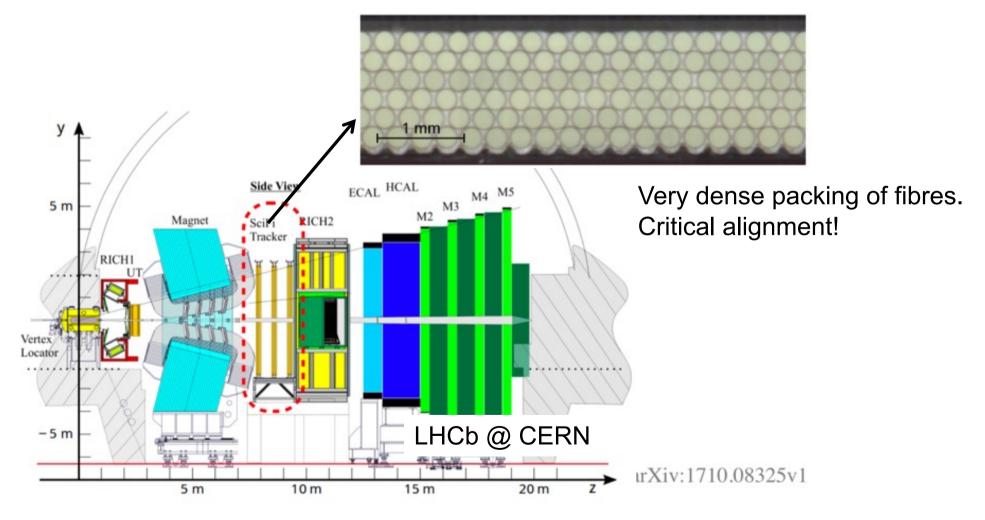

# 5: Group Readout: Clusters & Time

Example: 'Scintillating Fibre Tracker' of LHCb

Fermilab ASIC Department Talk: SPADs for fundamental research

UNIVERSITÄT

HEIDELBERG

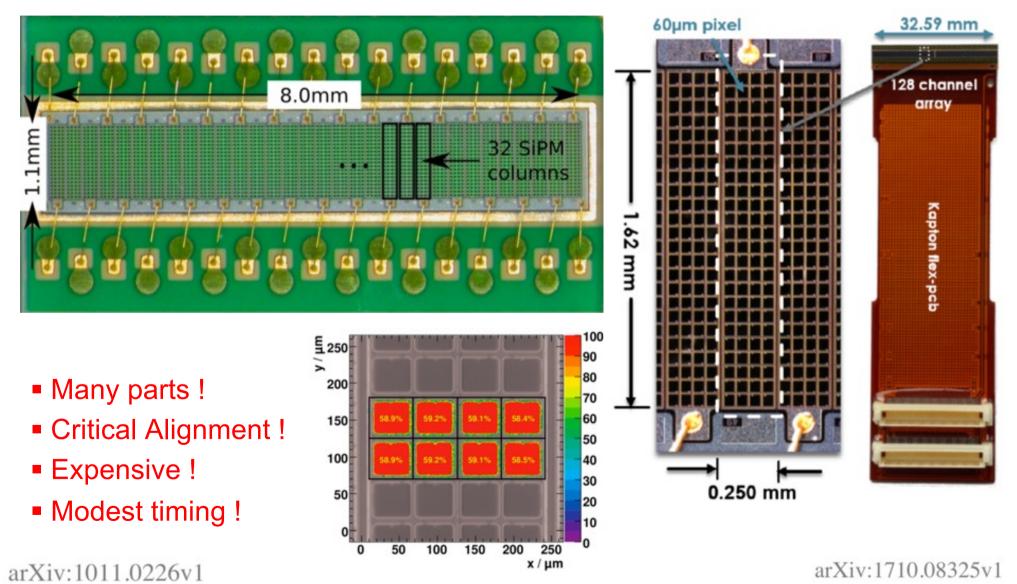

## 5: How is it done so far?

UNIVERSITÄT HEIDELBERG

#### SiPM Arrays + Boards + Cables + dedicated ASICs (e.g. PACIFIC in LHCb)

Fermilab ASIC Department Talk: SPADs for fundamental research

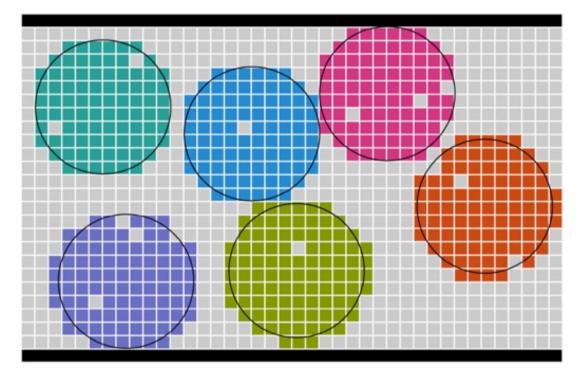

# 5: New concept: Group Readout Architecture

UNIVERSITÄT HEIDELBERG

#### Architecture allows to freely group pixels. Hits per group are 'counted'

- Alignment (of fibres) fully uncritical

- No dark noise from 'unused' SPADs

- Simple system with only one sensor + chip

- Good timing (tbc.)

- Cheap

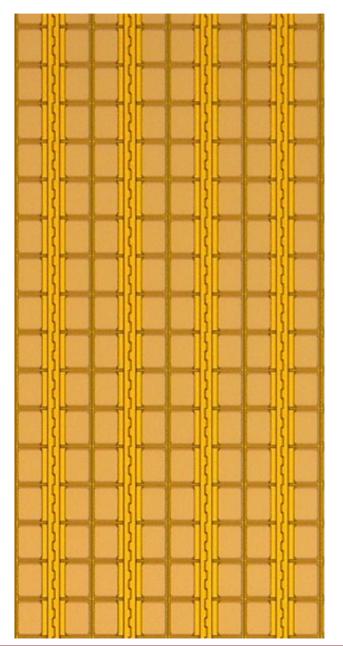

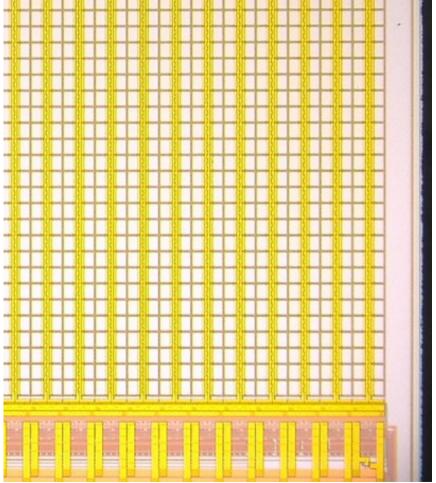

# 5: Group Chip

- Pixels of 42 / 56 µm size (2 different chips)

- ~65% fill factor (better than SiPM!)

- Sensitive area: H=1-2mm, W arbitrary

- Time and energy measurement

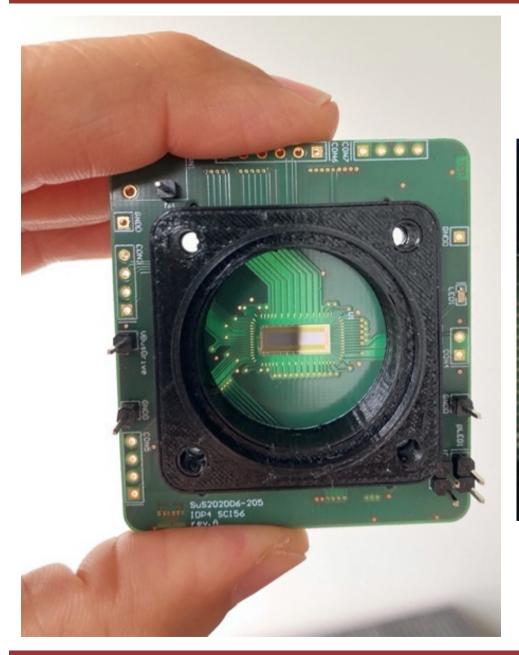

# 5: Chip Boards

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

Fermilab ASIC Department Talk: SPADs for fundamental research

P. Fischer, Heidelberg University, Page 48

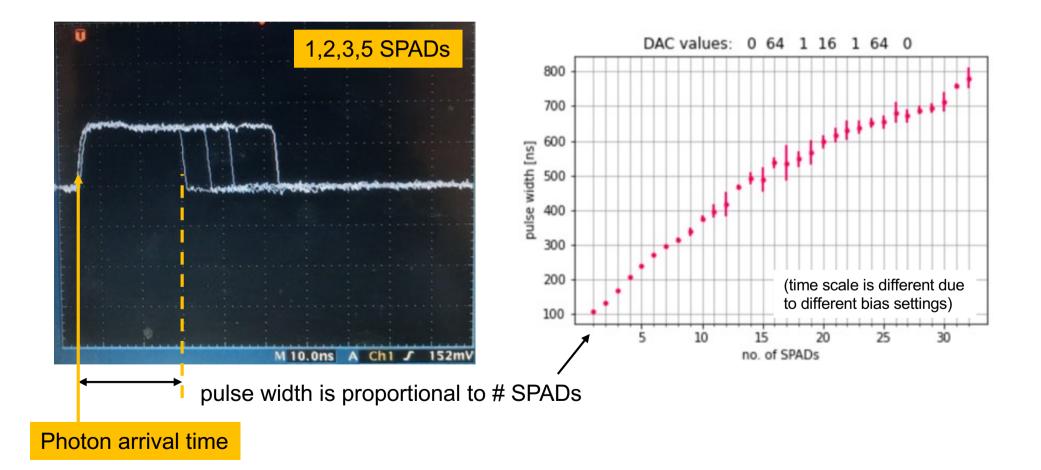

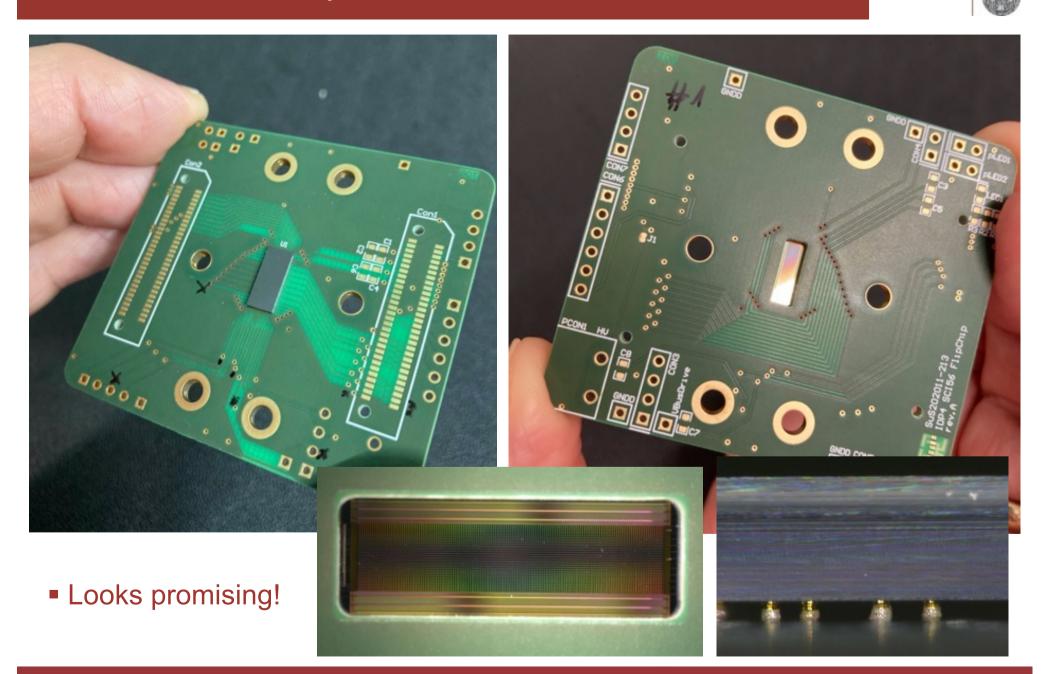

#### 5: Results

- Chips work as expected.

- Can extract group multiplicity from a single pulse-width coded output

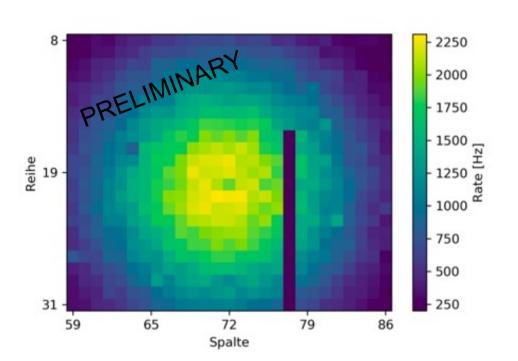

# 5: Application: First Fibre Readout

- By BSc Benedict Maisano (Physics Institute Heidelberg)

- Test1: Single scintillating fiber illuminated with radioactive source

- Results as expected

UNIVERSITÄT HEIDELBERG

## 5: Realistic Test

- Fiber mat (bundle)

- Very nice result

- Measurements still slow

- Pulse width measured using scope

- Better FPGA firmware close to ready

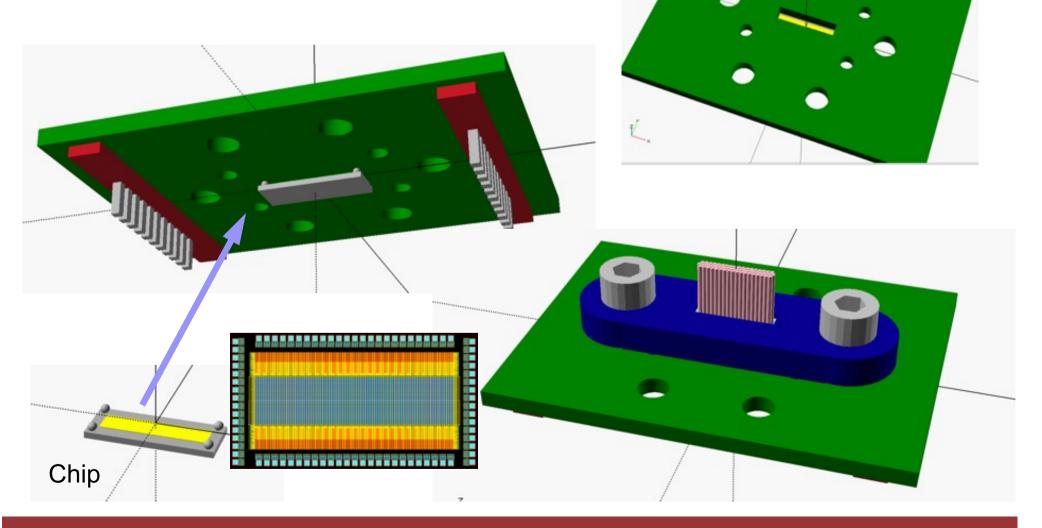

## 5: Next Step in Mechanics

- Try to use bump bonded & flipped chip

- Fiber inserted in PCB hole

Fermilab ASIC Department Talk: SPADs for fundamental research

## 5: Brand New: Fully assembled boards

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

Fermilab ASIC Department Talk: SPADs for fundamental research

P. Fischer, Heidelberg University, Page 53

#### Summary

- CMOS SPADs may enable better detector systems !

- Advantages are

- Very simple system (detection and readout on one piece of silicon)

- Low power

- Low cost

- High spatial and time resolution

- Low intrinsic activity

- ...

- Drawbacks

- Reduced fill factor for complex architectures (but SiPMs do not have 100%!!)

- SPAD properties (DCR, QE) not as 'optimized' as in pure SiPMs (but we are close, and vendors can improve things, if pushed...)

- Fun! Hopefully many exciting applications! Looking for Cooperations!

# Thanks for your attention!

Fermilab ASIC Department Talk: SPADs for fundamental research

P. Fischer, Heidelberg University, Page 55